※本セミナはZoomを使ったオンライン限定セミナです.

詳細は,オンライン限定セミナについてをお読みください.

ディープラーニングの「推論モジュール」のHDL化にひとまず成功したとしよう.しかし,そのモジュールにどのようにMNISTのような手書き文字画像データを入力したら良いのか?またHDL化の最大のメリット「高速化」を実感するには,入力は静止画ではなく「動画」である必要がある.

また,推論モジュールの出力をどのように表示したら良いのか?カメラ動画とともにリアルタイムで推論結果を表示し,正解不正解を目視する仕組みも必要である.

本セミナでは,CMOSカメラ(イメージセンサ)からの動画をリアルタイムにCNN(畳み込みニューラルネットワーク)推論モジュールに入力する技術,推論モジュールの出力をカメラ動画とともに1台のVGAに映し出す技術を説明する.

本セミナではCNN編でHDL化した推論モジュールをDE1-SoCというFPGAボードにプログラムし,黒板にチョークで書いた文字を認識させる.推論モジュール自体の説明,Python→HDL化の方法論は

CNN編または

入門編で行う(いずれのセミナも特殊なIPコアや高位合成などは使わずに「力技」でHDL化する).講師サイト(下記参照)の「第3部 FPGA+CMOSカメラでリアルタイム画像認識」のセミナ版.

※「カメラ取り付け用アダプタボード」は下記サイトから販売予定.

Http://digitalfilter.shop-pro.jp/

●対象聴講者

・電気製品にディープラーニングを組み込みたい人

・ディープラーニングを高速化,低消費電力化したい人

・FPGAに興味がある人

・PythonやC言語で書かれたアルゴリズムをHDL化したい人

講師サイトに目を通しおくとベター

●講演の目標

・大量な積和演算を必要とするアルゴリズムを実装する際,CPUやGPUの他に「FPGA」という選択肢が一つ増える

・並列化,パイプライン化ができるのでCPUより高速化が可能であり,GPUと比べて低消費電力になる

・CMOSカメラからの動画をディープラーニング推論モジュールに入力する方法が分かる

・ディープラーニング推論モジュールの出力をVGAに表示する方法が分かる

・FPGAの限られたリソースを効率良く使う方法,回路規模削減方法が分かる

・ロジックアナライザでFPGA内部信号を確認し,正常動作しているかを確認できる

・SDRAMを使ってCMOSカメラとVGAの同期をとる方法がわかる

●内容

1 とりあえず動かしてみる

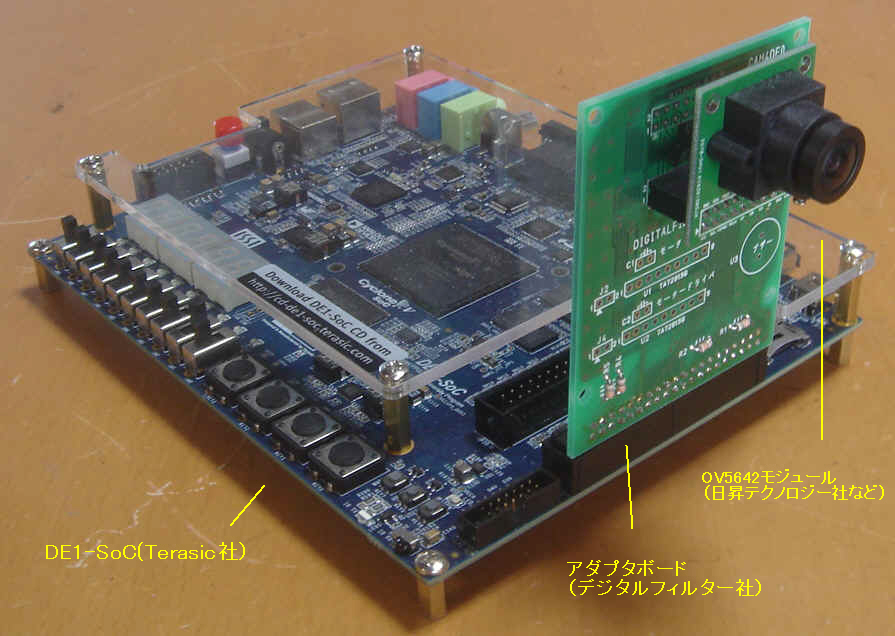

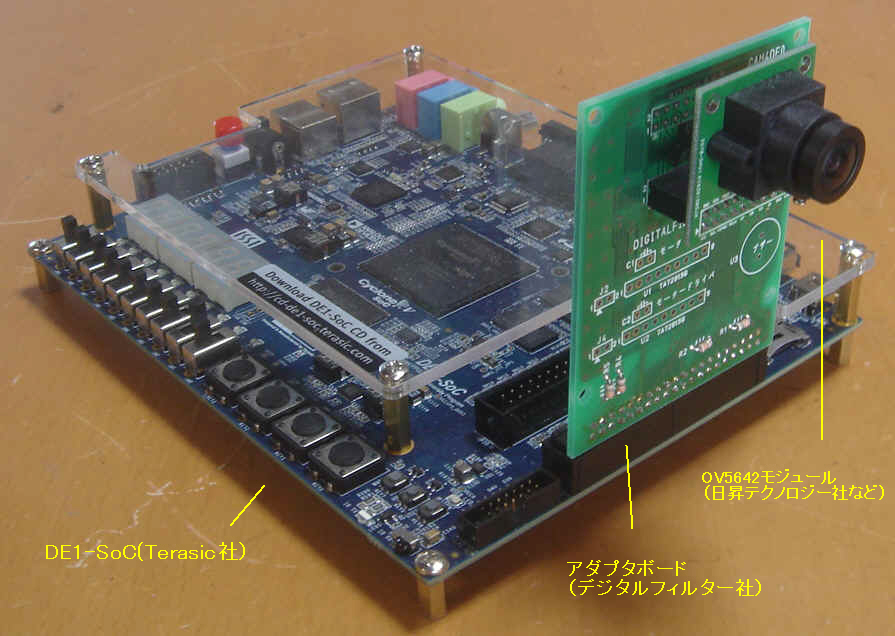

1.1 OV5642カメラモジュール+アダプタボード+FPGAボード

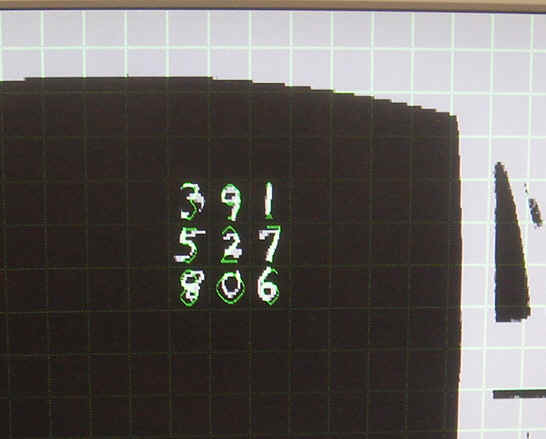

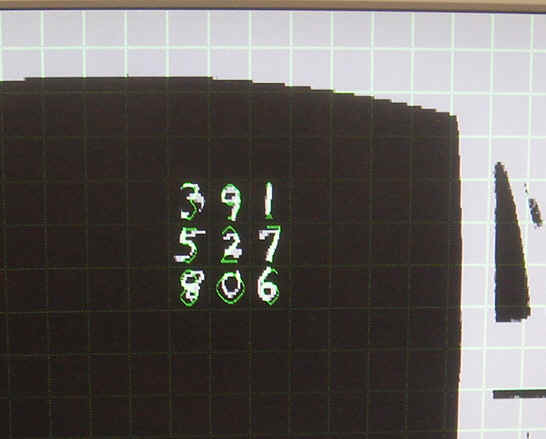

1.2 黒板にチョークで文字を書いてカメラの前にかざして推論

2 論理合成する前にPythonで正解率を確認

2.1 FPGAでは小数は使えないので整数化する(正解率99.35→98.84%)

2.2 2層目以降の係数を4種類にしてシフト乗算(正解率98.28%)

2.3 2層目以降の画素を16段階にしてビット幅削減(正解率98.53%)

3 FPGAに入りきるかどうか論理合成してみる

3.1 そのままだとRAMに割り当てられず回路規模が爆発する

3.2 重み係数を2ビットにエンコード

3.3 M10k(メモリブロック)を効率よく使う

4 まずはCMOSカメラなしでFPGAに焼いてみる

4.1 ROM内にあるMNIST最初の8枚を繰り返し入力する

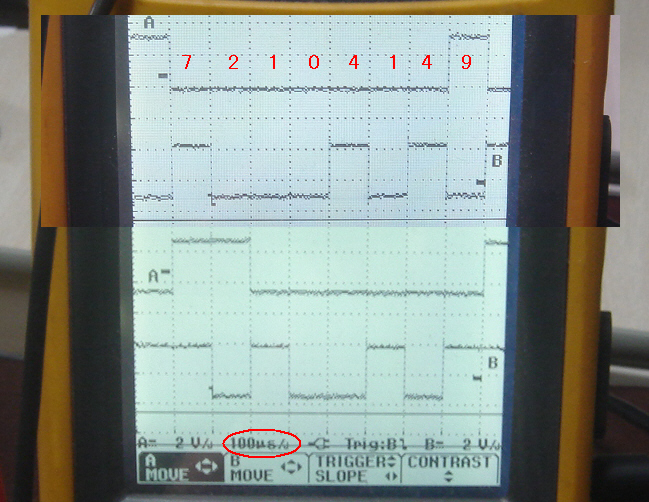

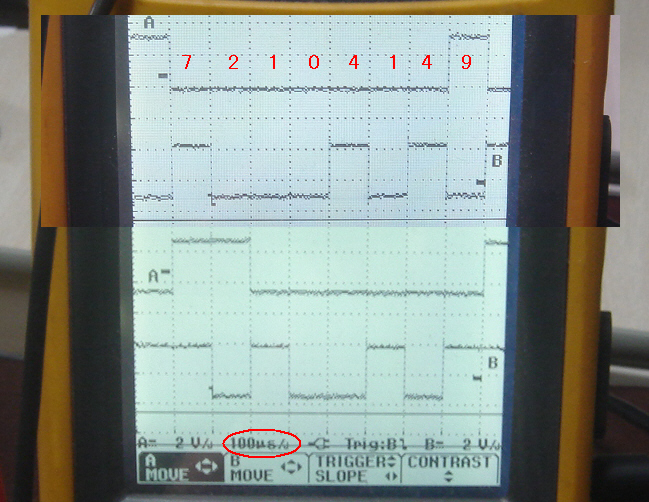

4.1 クロック100MHz(10ns)で推論できているかオシロで確認

4.2 FPGA内部の演算をロジックアナライザで確認

5 CMOSカメラでVGAに動画を映す

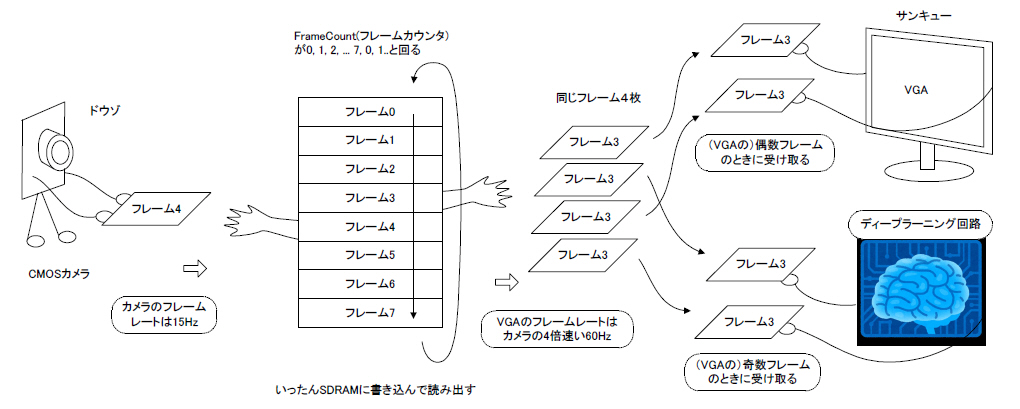

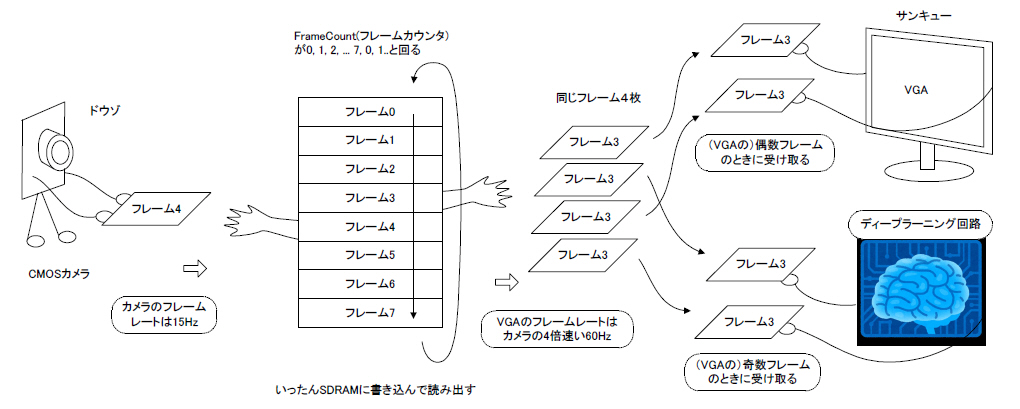

5.1 CMOSカメラの動画をVGAに映すにはSDRAMが必須

5.2 Quartusでハードを,NiosII SBTでソフトを書き込み

5.3 動画を映すための各HDLモジュールの役割

6 CNNモジュールの入出力インターフェース

6.1 画像の入力の仕方

6.2 推論結果の出力の仕方

7 CMOSカメラからの動画をリアルタイムに推論させる仕組み

7.1 動画と推論結果,両方VGAに映すには・・・

7.2 VGAを細かいブロックに分割する

7.3 各ブロックを順番にCNNモジュールに送る

8 推論結果をVGAに重ね書きさせる仕組み

8.1 10個の数字パターンを格納するROM

8.2 推論結果に対応するビットを取り出す

8.3 動画フレームと推論結果フレームを交互に表示

9 まとめ

9.1 手仕上げHDLのメリット~高速,コンパクト,低消費電力

9.2 手仕上げHDLのポイント~整数化,ビットシフト乗算,並列化,パイプライン化,Excel+VBAによる自動生成

●講演の参考文献,参考URL

1. 講師サイト:http://digitalfilter.com/deeponhw/deeponhw01.html

2.

ゼロから作るDeep Learning,オライリー.この書籍の8章,242ページにあるPythonプログラムをHDL化する

FPGAボード+アダプタボード+CMOSカメラモジュール

FPGAボード+アダプタボード+CMOSカメラモジュール

推論結果が緑色で重ね書きされる

推論結果が緑色で重ね書きされる

正しい推論結果が100us周期で出てくる

正しい推論結果が100us周期で出てくる

代わりばんこにフレームを渡す OV5642からの動画をVGAに映す手順(動画ではQuartus18.1ですがセミナでは19.1を使います)OV5642からの動画をリアルタイム推論

代わりばんこにフレームを渡す OV5642からの動画をVGAに映す手順(動画ではQuartus18.1ですがセミナでは19.1を使います)OV5642からの動画をリアルタイム推論