※本セミナはZoomを使ったオンライン限定セミナです.

詳細は,オンライン限定セミナについてをお読みください.

畳み込みニューラルネットワーク(Convolutional Neural Network, CNN)のハードウェア化に挑戦する.特殊なIPコアや高位合成などは使わずに「力技」でHDL化する.

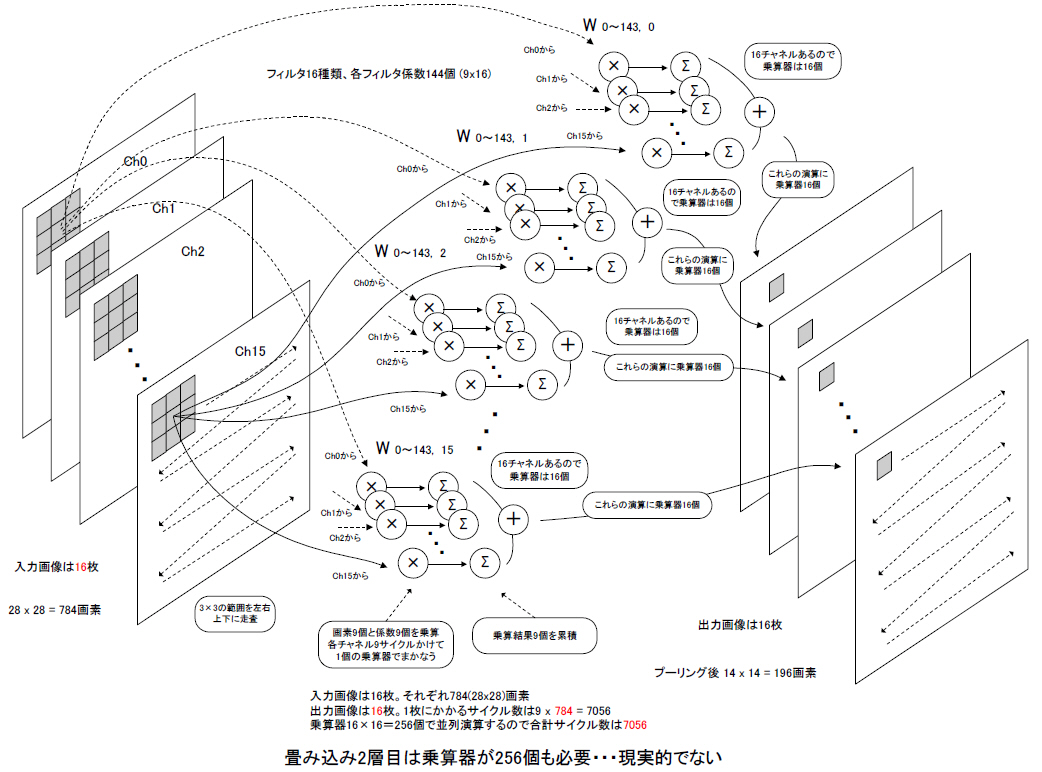

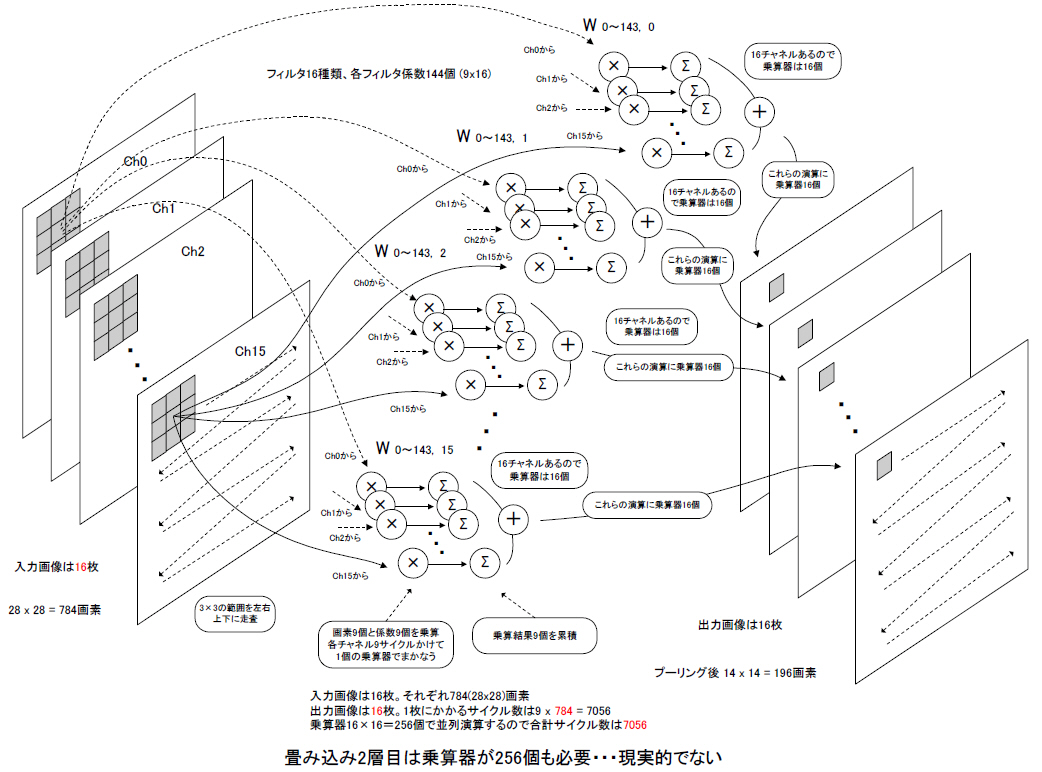

ディープラーニングには「全結合ニューラルネットワーク」や「畳み込みニューラルネットワーク(CNN)」といった手法があるが,本セミナでは後者で「推論」を行う.CNNは正解率が高くなるが(MNISTという手書き数字画像データセットで98%以上),そのぶん演算量が増えて複雑になる.

CNNのプログラムはPythonで書かれており,畳み込みが6層,Affineが2層と多層にわたるが,一つずつ丁寧にExcel化,HDL化する.その後論理シミュレーションし,Pythonと結果が一致することを確認する.

CNNは重み係数が膨大になるが,FPGAで使用できる乗算器には限りがあるので,「ビットシフト」により「乗算器を使わない乗算」を行う.また重み係数のHDLファイルはExcel+VBAで自動生成させる.

講師サイト(下記参照)の「第2部 畳み込みニューラルネットワーク」のセミナ版.本セミナは論理シミュレーションまでだが,その続きとして,FPGA上でCMOSカメラからの動画を処理する

リアルタイム推論編も用意している.

●対象聴講者

・電気製品にディープラーニングを組み込みたい人

・ディープラーニングを高速化,低消費電力化したい人

・FPGAに興味がある人

・PythonやC言語で書かれたアルゴリズムをHDL化したい人

講師サイトに目を通しおくとベター

●講演の目標

・大量な積和演算を必要とするアルゴリズムを実装する際,CPUやGPUの他に「FPGA」という選択肢が一つ増える

・並列化,パイプライン化ができるのでCPUより高速化が可能であり,GPUと比べて低消費電力になる

・PythonやC言語で書かれたアルゴリズムをハードウェア化する手順が分かる

・回路のどの部分を「並列化」すれば高速化できるかの勘所が分かる

・「パイプライン化」のイメージとその効果をつかめる

・FPGAの乗算器が足りないときの対処法が分かる

・特殊なIP,ライブラリ,高位合成ツールを使わず,FPGAベンダ・デバイスに依存しないHDLを作成する

●内容

1 畳み込み1層目のハードウェア化

1.1 畳み込みニューラルネットワークとは

1.2 パディングで拡げてから畳み込み

1.3 まずは小数で畳み込みニューラルネットワーク(正解率99.35%)

1.4 整数化してもほとんど正解率が落ちない!(正解率98.84%)

1.5 im2col関数をどう実現するか

1.6 畳み込みの回路図とタイムチャート

1.7 VHDLを書いたり自動生成したり

1.8 シミュレーションがPythonやExcelと合っているか確認

2 畳み込み2層目のハードウェア化

2.1 2層目は乗算器が256個も必要になる?

2.2 係数が4種類しかなくても98%以上!(正解率98.28%)

2.3 乗算器の代わりになる回路の設計

2.4 畳み込み2層目を論理シミュレーション

3 畳み込み3~6層目のハードウェア化

3.1 VBAを駆使して3層目をExcel化する

3.2 VBA+Excelで4,5,6層目を計算させる

3.3 3層目は乗算器128個で4回に分けて計算

3.4 3層目の画像の読み出し・書き込み

3.5 3層目のVHDLファイル自動生成(Excel+VBA)

3.6 3層目の論理シミュレーション

3.7 4,5,6層目の演算イメージ

3.8 4,5,6層目の画像の読み出し・書き込み

3.9 4,5,6層目のVHDLファイル自動生成(Excel+VBA)

3.10 4,5,6層目の論理シミュレーション

4 Affine1~2層目のハードウェア化

4.1 Affine(全結合)層をExcel化する

4.2 Affine1,2層目のVHDLファイル自動生成(Excel+VBA)

4.3 Affine1,2層目の行列乗算

4.4 Affine1層目の論理シミュレーション

4.5 Affine2層目で「畳み込みニューラルネットワーク」は終わり

5 全層繋いでシミュレーション

5.1 非パイプラインで全層繋ぐ(層レベルでは逐次処理)

5.2 パイプラインで全層繋ぐ(層レベルでも並列処理)

5.3 CNN(畳み込み6層+Affine2層)のスループットが10kサイクル!

●講演の参考文献,参考URL

1. 講師サイト:http://digitalfilter.com/deeponhw/deeponhw01.html

2.

ゼロから作るDeep Learning,オライリー.この書籍の8章,242ページにあるPythonプログラムをHDL化する

CNNは係数が膨大なので工夫が必要

CNNは係数が膨大なので工夫が必要

係数を4種類にしてビットシフトで乗算を行う

係数を4種類にしてビットシフトで乗算を行う

係数を4種類にしても正解率98%以上

係数を4種類にしても正解率98%以上

スループットは100us(10kサイクル@CLK10ns)整数化すればPythonとExcelとHDLの結果は同じになる数千個に及ぶHDLファイルをExcel+VBAで自動生成

スループットは100us(10kサイクル@CLK10ns)整数化すればPythonとExcelとHDLの結果は同じになる数千個に及ぶHDLファイルをExcel+VBAで自動生成