※本セミナはZoomを使ったオンライン限定セミナです.

詳細は,オンライン限定セミナについてをお読みください.

FPGAは100MHz程度で動かすため,GPUと比べて消費電力は1桁小さく,「AIチップ」の有力候補である.

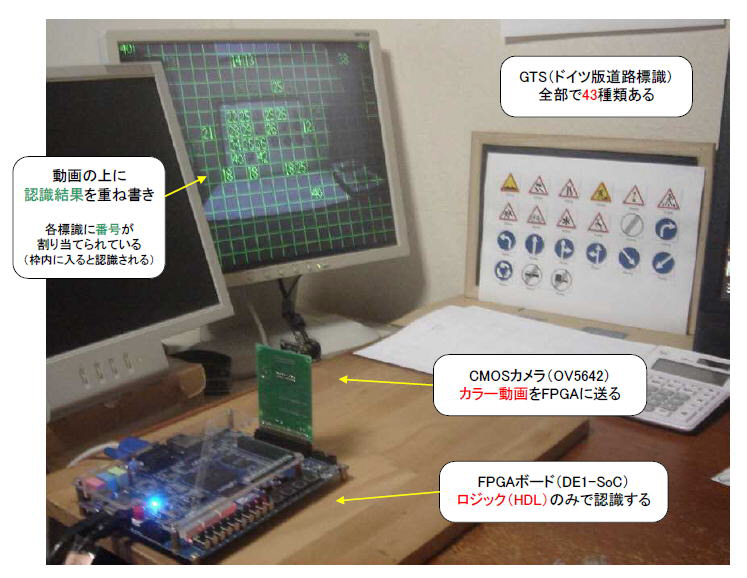

本セミナでは「畳み込みニューラル・ネットワーク(CNN)のハードウェア推論IP」を活用し,CMOSカメラ・モジュールからのカラー動画をリアルタイム認識する.言わば,推論IPの「使い方」がテーマのセミナである.したがって,HDLの知識がないソフト系エンジニアでも活用できる内容となっている.推論IPはあらかじめ用意されたもので,HDLで書かれている.特殊なライブラリや高位合成などは使わない純粋なRTL記述になっており,特にベンダを選ばないが,さしあたりDE1-SoCというボードに搭載のIntel-FPGAに実装する.

GTSRBというドイツ道路標識データセットを使い,まずはPythonで学習モデルを作る.その後,Excel+VBAで重み係数やバイアスなどのHDLを自動生成する.それらを推論IPとともに論理合成すれば「道路標識のリアルタイム認識システム」が完成する.

推論結果はモニタ上の動画に上書きされ,正解不正解を目視で確認できる.また同じ推論IPを複数の認識対象にも活用できる.

さらに,Kaggle(AI技術者の集い場)にある「信号機」のデータセットを使って学習モデルを新たに作成し,同様にFPGAに実装すれば「信号機の認識システム」となる.

「作り方」に関しては別セミナ

FPGAで作る!省電力エッジAIチップ?ハードウェア推論IP【作成編】を用意している.

●対象聴講者

・電気製品にディープラーニングを組み込みたい人

・ディープラーニングを高速化,低消費電力化したい人

・FPGAに興味がある人

・Pythonで書かれたアルゴリズムをHDL化したい人

・動画のリアルタイム認識がしたい人

講師サイト(後述)に目を通しおくと理解の助けになる

●講演の目標

・大量な積和演算を必要とするアルゴリズムを実装する際,CPUやGPUの他に「FPGA」という選択肢が一つ増える

・並列化,パイプライン化ができるのでCPUより高速化が可能であり,GPUと比べて低消費電力になる

・Pythonで書かれたアルゴリズムをハードウェア化する手順が分かる

・特殊なライブラリ,高位合成ツールを使わず,FPGAベンダ・デバイスに依存しないHDLを作成する

・一つの推論IP(HDL)を複数の認識対象に使い回せる

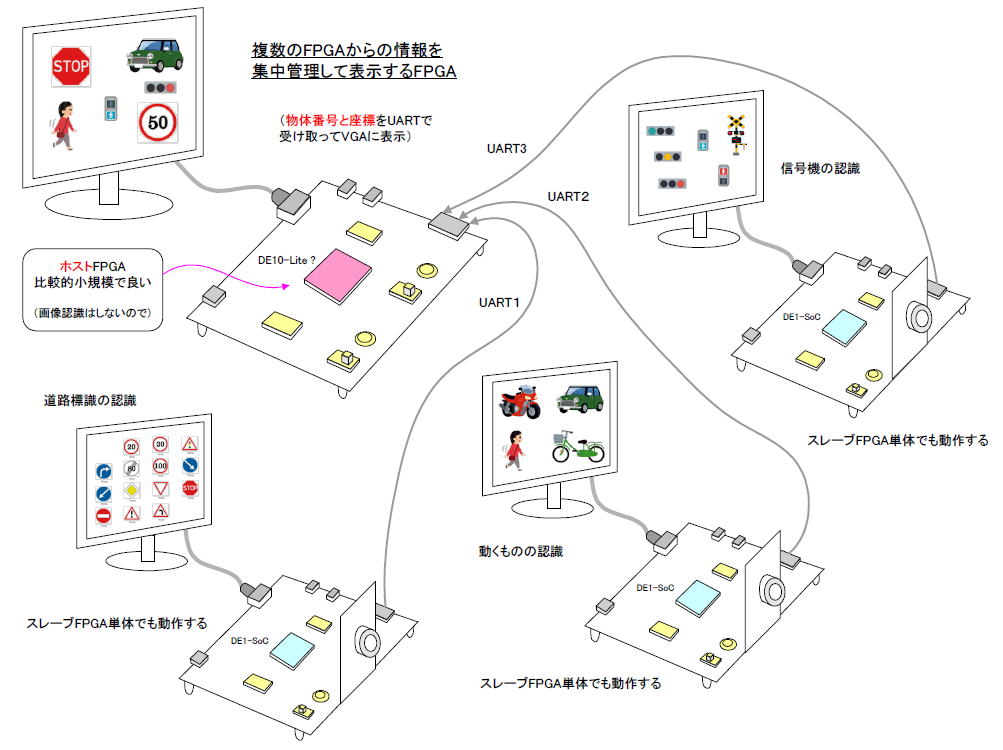

・複数の認識対象を複数のFPGAで処理してマイコン等で集中管理することも可能

●内容

1 推論IPを使ってみる~本セミナの最終目標

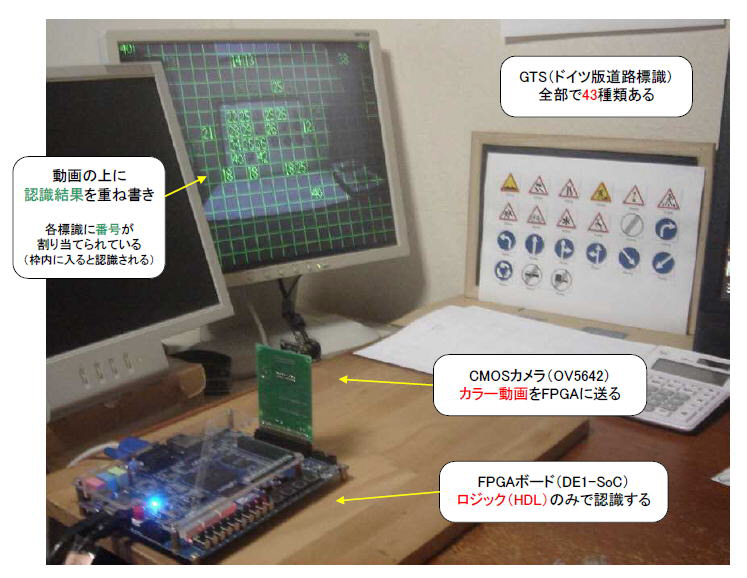

1.1 道路標識の認識をハードウェア化してみた

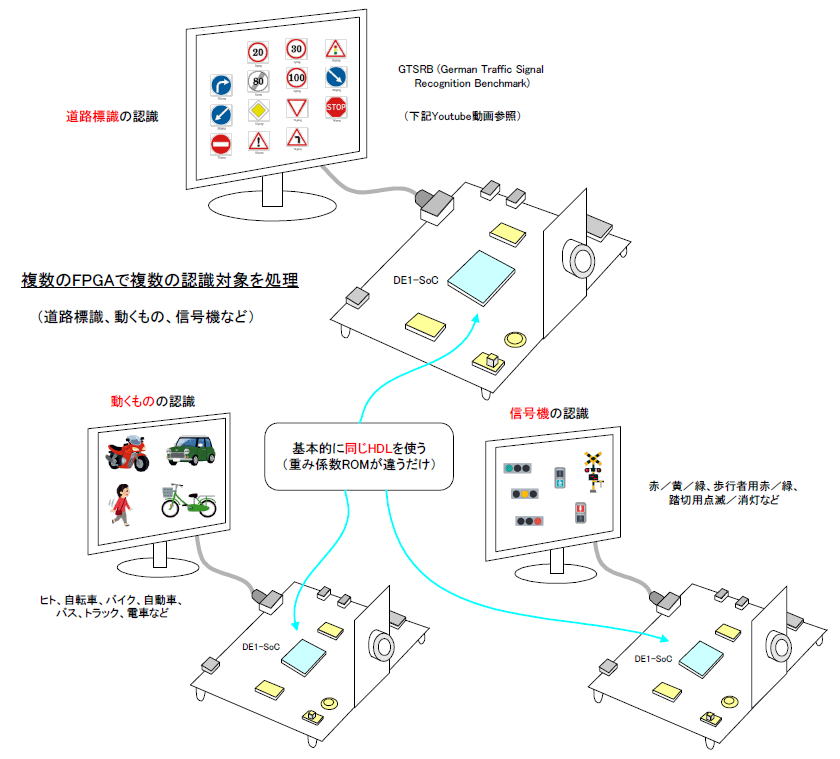

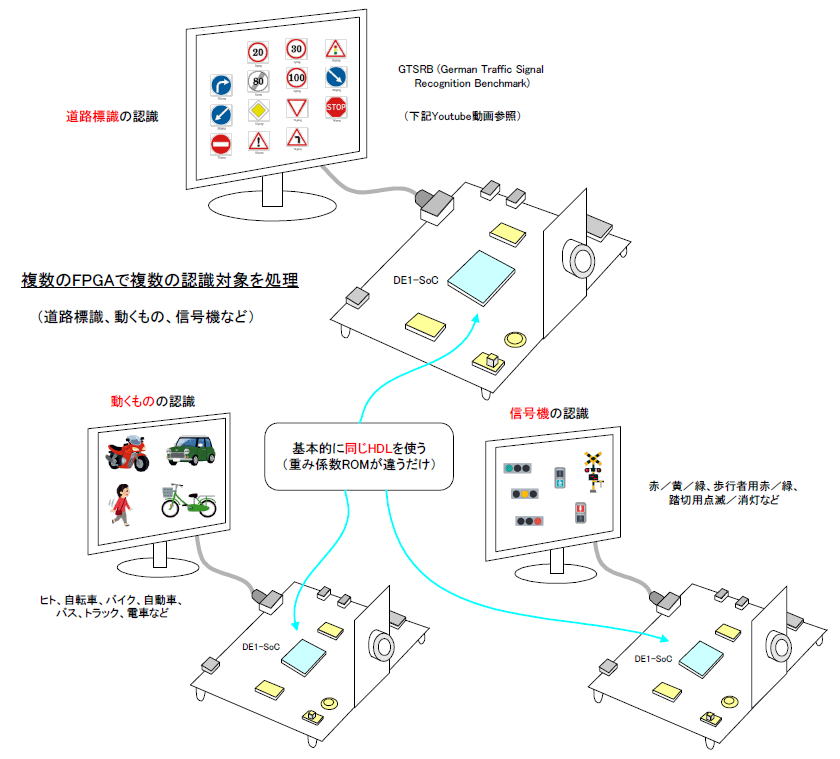

1.2 同じ推論IP(HDL)を複数の認識対象に使い回す

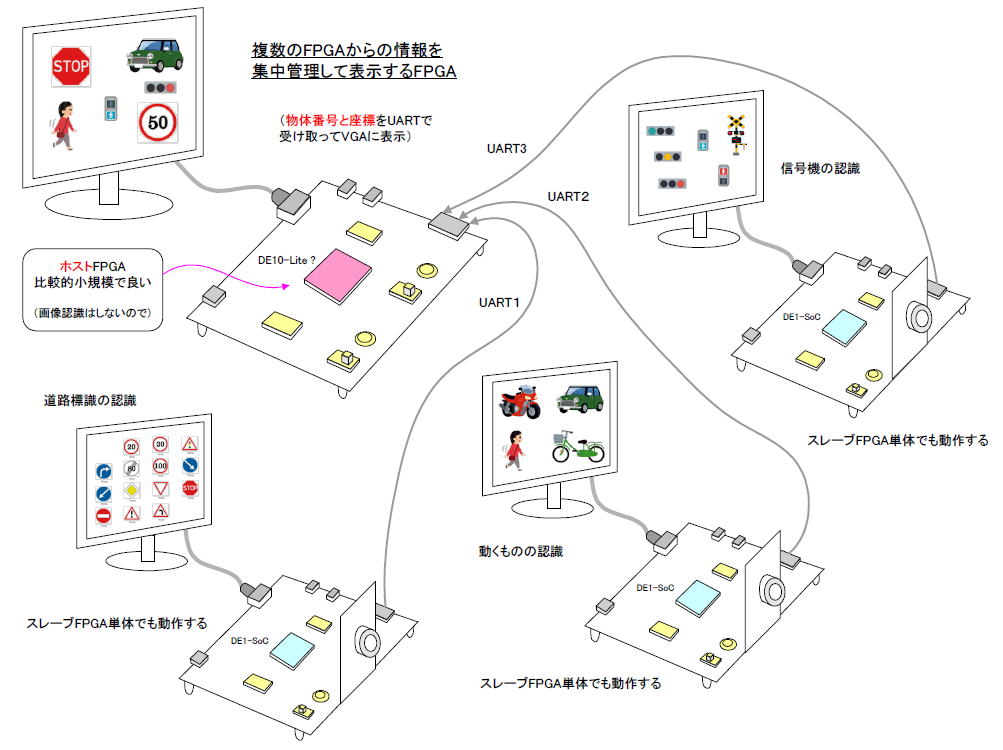

1.3 複数のFPGAからの情報を集中管理するFPGA/マイコン

2 学習モデルの作成

2.1 世界中のAI研究者が集うKaggle!

2.2 道路標識のデータセットGTSRB

2.3 学習→推論してみる(認識率98%台)

2.4 畳み込み4層+全結合2層で認識

2.5 ハードウェア化を見据えたモデルの作成

2.6 学習から推論まで,Pythonコードの流れ

2.7 学習済みモデル(係数とバイアス)のセーブ

3 ハード化を見据えてPythonの変更

3.1 画像データの整数化(量子化)

3.2 1層目,6層目の係数とバイアスの整数化

3.3 2層目は係数8種,ビットシフトで乗算器を節約

3.4 3, 4, 5層目は係数を4種にしてROMを節約

3.5 整数化したPythonで認識率97%台

3.6 画像データのビット数を削減してレジスタやRAMの節約

3.7 Pythonの変更はこれで終了(認識率95%台)

4 PythonをExcelに移植する

4.1 本セミナのロードマップ

4.2 1層目のExcel化

4.3 2層目のExcel化

4.4 3, 4層目のExcel化

4.5 5, 6層目のExcel化

5 VBAを使って楽をしよう

5.1 重み係数とバイアスのHDL生成

5.2 カメラエミュレータROMのHDL生成

5.3 推論ラベルパターンROMのHDL生成

6 FPGAに実装

6.1 Quartus Prime

6.2 Platform Designer

6.3 NiosII SBT

6.4 Signal Tap Logic Analyzer

7 今度は「信号機」の認識!

7.1 Pythonで信号機データセットを学習させる

7.2 重み係数とバイアスをExcelにコピペ

7.3 VBAで重み係数とバイアスのHDL生成

7.4 重み係数とバイアスを置き換えてFPGAに実装

コラム 画像クラスを複数のFPGAで分担して認識率UP

●講演の参考文献,参考URL

1. 講師サイト:http://digitalfilter.com/gtsonhw/gtsonhw01.html

道路標識のリアルタイム認識-FPGAで作る省電力エッジAIチップ

道路標識のリアルタイム認識-FPGAで作る省電力エッジAIチップ

ニューラルネットワークの形状を共通化した結果HDLを使い回せる

ニューラルネットワークの形状を共通化した結果HDLを使い回せる

FPGAによる画像認識統括システム

FPGAによる画像認識統括システム

GTSRB画像.この例では2枚不正解(赤線)

GTSRB画像.この例では2枚不正解(赤線)

VGA画面.30x30の格子に入ったら認識される(背景にうっすらと標識が見える)ロジックのみで省電力!組み込み用AIチップ道路標識の認識を信号機の認識に変更認識結果をUARTでホストFPGAに送る

VGA画面.30x30の格子に入ったら認識される(背景にうっすらと標識が見える)ロジックのみで省電力!組み込み用AIチップ道路標識の認識を信号機の認識に変更認識結果をUARTでホストFPGAに送る