●対象聴講者

・ある程度HDLが理解できる人(ハード系エンジニア向け)

・電気製品にディープラーニングを組み込みたい人

・ディープラーニングを高速化,低消費電力化したい人

・FPGAに興味がある人

・Pythonで書かれたアルゴリズムをHDL化したい人

・動画のリアルタイム認識がしたい人

講師サイト(後述)に目を通しおくと理解の助けになる

●講演の目標

・大量な積和演算を必要とするアルゴリズムを実装する際,CPUやGPUの他に「FPGA」という選択肢が一つ増える

・並列化,パイプライン化ができるのでCPUより高速化が可能であり,GPUと比べて低消費電力になる

・Pythonで書かれたアルゴリズムをハードウェア化する手順が分かる

・特殊なライブラリ,高位合成ツールを使わず,FPGAベンダ・デバイスに依存しないHDLを作成する

・一つの推論IP(HDL)を複数の認識対象に使い回せる

・複数の認識対象を複数のFPGAで処理してマイコン等で集中管理することも可能

●内容

1 推論IPを使ってみる~本セミナの最終目標

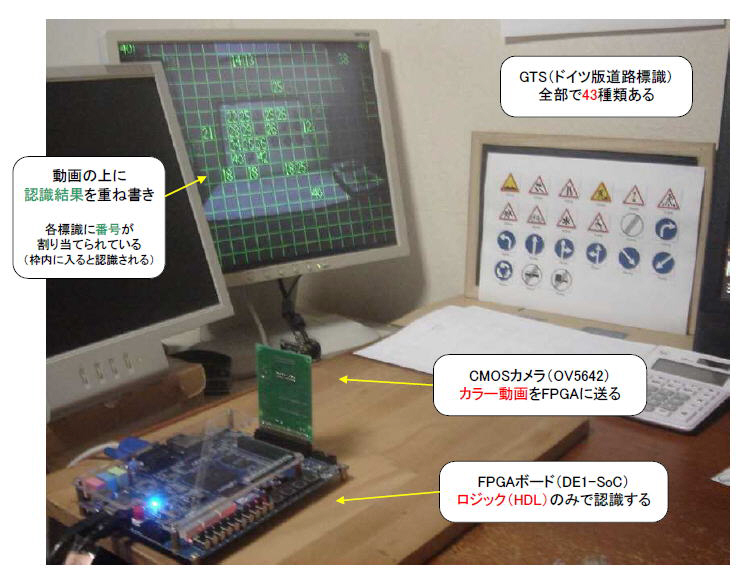

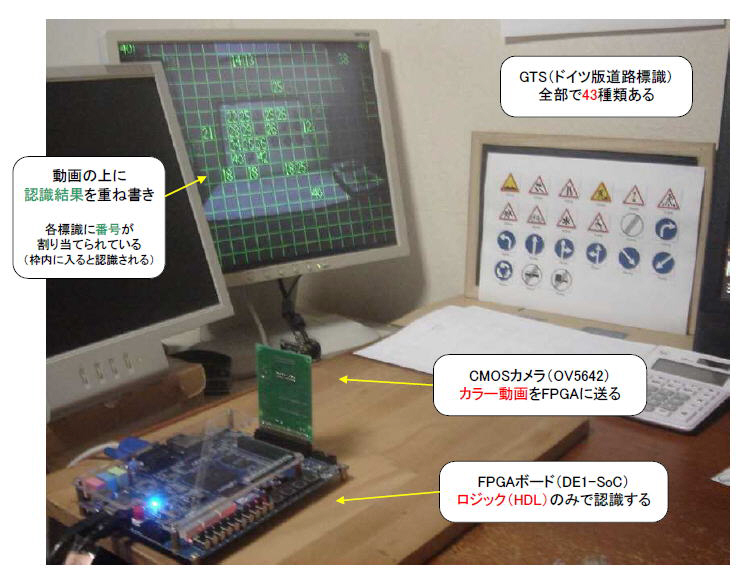

1.1 道路標識の認識をハードウェア化してみた

1.2 同じ推論IP(HDL)を複数の認識対象に使い回す

1.3 複数のFPGAからの情報を集中管理するFPGA/マイコン

2 PythonからExcelまで

2.1 本セミナのロードマップ

2.2 Pythonを走らせる(小数→整数化により認識率98→95%台)

2.3 PythonをExcelに移植する(整数なので結果はピタリ一致する)

3 HDLを書く前に決めておくこと

3.1 HDLの全体構成

3.2 畳み込み4層+全結合2層で認識

3.3 各層間のRAMを考える

3.4 各層の係数ROMを考える

3.5 スループットを決める

4 畳み込み1層目のHDL化

4.1 重み係数ROMのデータは9ビット(VBAで自動生成)

4.2 積和演算の回路図とタイムチャート

4.3 積和演算のHDLを書く

4.4 RAMアクセスの回路図/タイムチャート/HDL

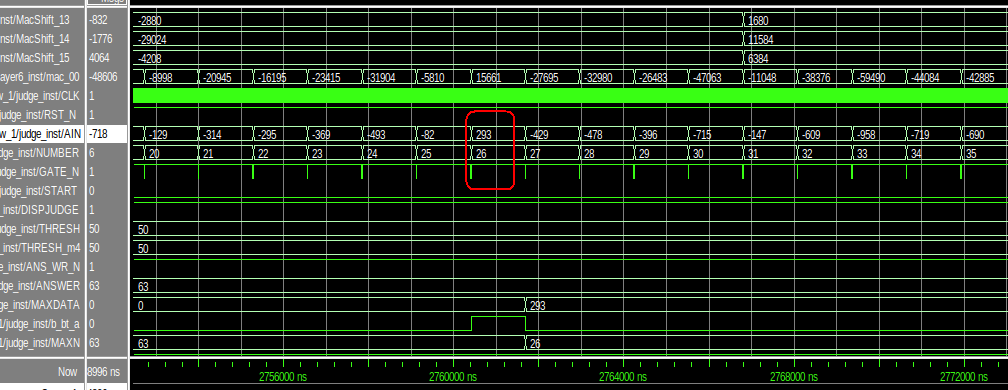

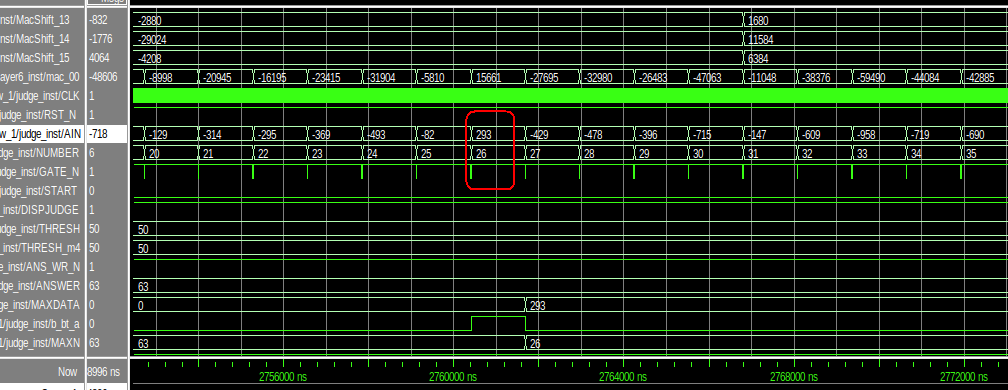

4.5 論理シミュレーションとPython/Excelの答え合わせ

5 畳み込み2層目のハードウェア化

5.1 重み係数ROMのデータは3ビット(VBAで自動生成)

5.2 乗算器を使わないビットシフト乗算

5.3 プーリング回路で出力を間引く

5.4 RAMアクセスの回路図/タイムチャート/HDL

5.5 論理シミュレーションとPython/Excelの答え合わせ

6 畳み込み3,4層目のハードウェア化

6.1 RAMアクセスの回路図/タイムチャート/HDL

6.2 論理シミュレーションとPython/Excelの答え合わせ

7 全結合5,6層目のハードウェア化

7.1 RAMアクセスの回路図/タイムチャート/HDL

7.2 論理シミュレーションとPython/Excelの答え合わせ

8 全層繋いでシミュレーション

8.1 パイプラインとは流れ作業のイメージ

8.2 各層間はRAM(ピンポンモード)で繋ぐ

8.3 論理シミュレーションとPython/Excelの答え合わせ

コラム FPGA実装の手順

●講演の参考文献,参考URL

1. 講師サイト:http://digitalfilter.com/gtsonhw/gtsonhw01.html

Pythonでの結果

Pythonでの結果

Excelでの結果がPythonと一致している

Excelでの結果がPythonと一致している

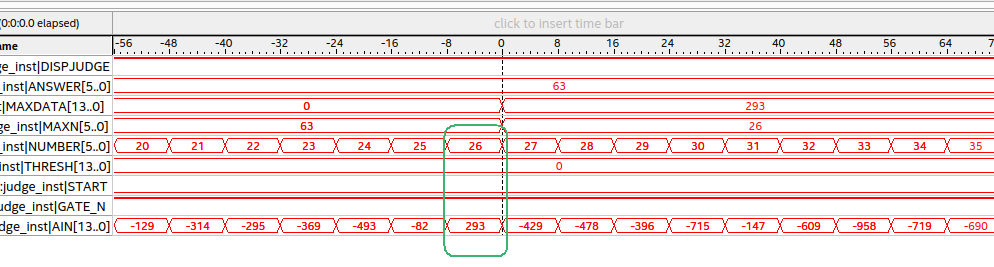

論理シミュレーションの結果がPythonと一致している

論理シミュレーションの結果がPythonと一致している

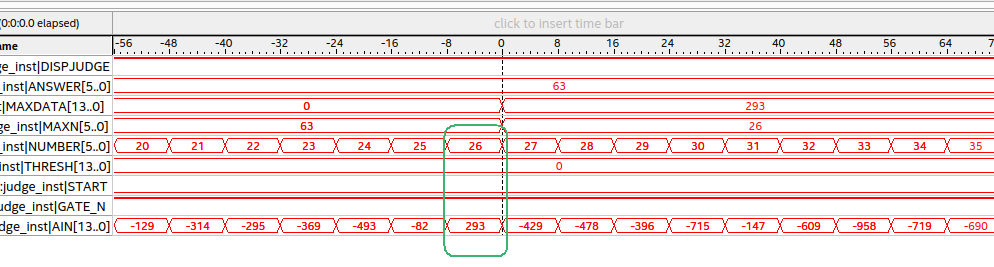

ロジックアナライザでFPGA内部を見るとPythonと一致している

ロジックアナライザでFPGA内部を見るとPythonと一致している

道路標識のリアルタイム認識-FPGAで作る省電力エッジAIチップロジックのみで省電力!組み込み用AIチップ道路標識の認識を信号機の認識に変更認識結果をUARTでホストFPGAに送る

道路標識のリアルタイム認識-FPGAで作る省電力エッジAIチップロジックのみで省電力!組み込み用AIチップ道路標識の認識を信号機の認識に変更認識結果をUARTでホストFPGAに送る