ディープラーニング ~ハードウェア化への道~入門編【オンライン限定セミナ】

ディープラーニング ~ハードウェア化への道~入門編【オンライン限定セミナ】

|

|

【開催日】2021年11月7日(日) 10:00-17:00 1日コース

【セミナNo.】ES21-0104 【受講料】25,000円(税込)

【会場】オンライン限定セミナ

【セミナNo.】ES21-0104 【受講料】25,000円(税込)

【会場】オンライン限定セミナ

申込締切は10月31日です.

※本セミナはGoogle Meetを使ったオンライン限定セミナです.

詳細は,オンライン限定セミナについてを参照ください.

ディープラーニング(全結合ニューラルネットワーク)のハードウェア化に挑戦する.特殊なIPコアや高位合成などは使わずに「力技」でHDL化する.

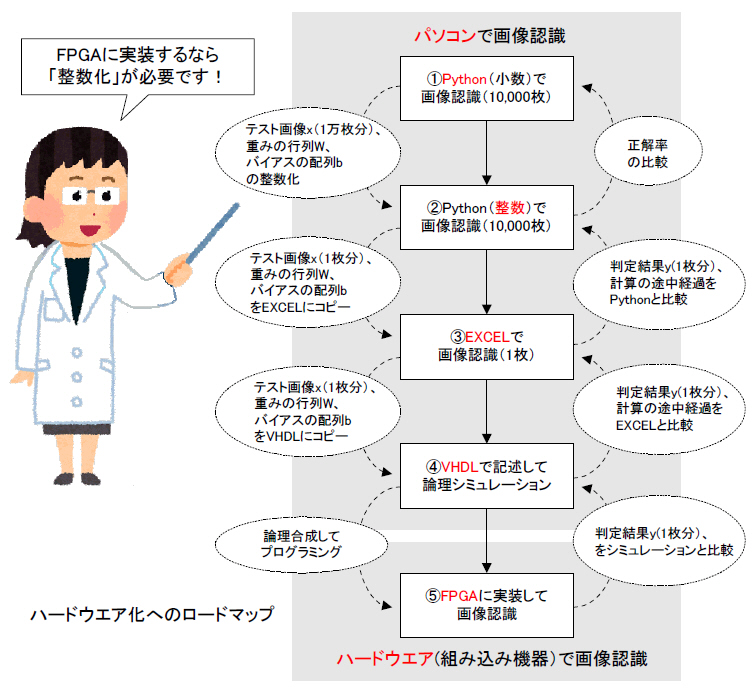

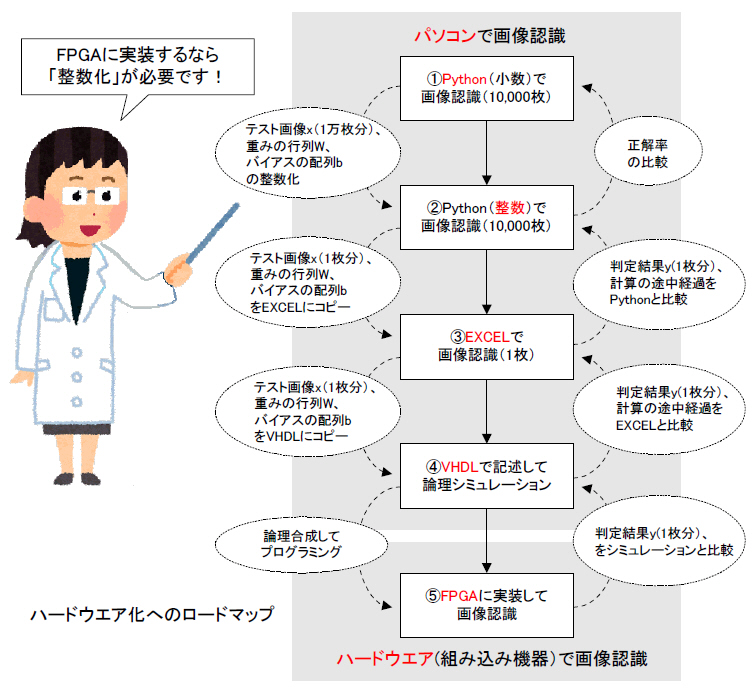

Pythonで書かれたMNISTという手書き数字画像データセットの「推論」プログラムを「整数化」して正解率がどの程度落ちるか確認する.その後重み係数や画像データをExcelに貼り付け,結果・途中経過がPythonと一致することを確認する.

その後は回路図を描き,タイムチャートでその動作を吟味した後,回路をHDL化する.その後論理シミュレーションを行い,結果・途中経過がExcelとピタリ一致することを確認する.さらに並列化,パイプライン化によって高速化する(サイクル数1/40以下).

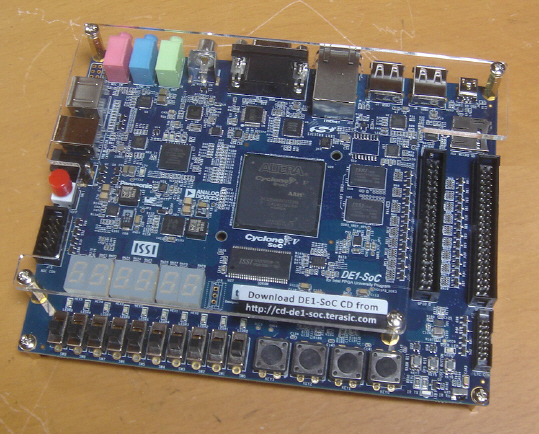

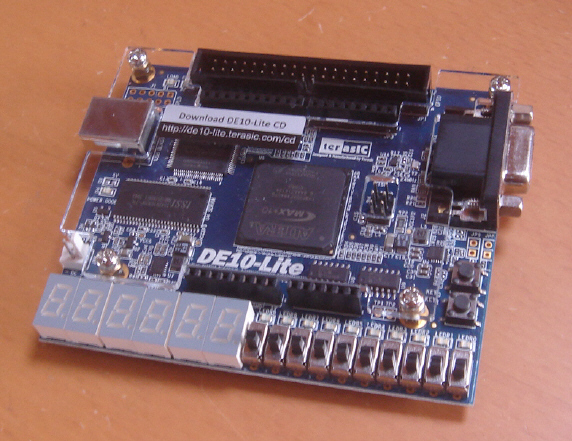

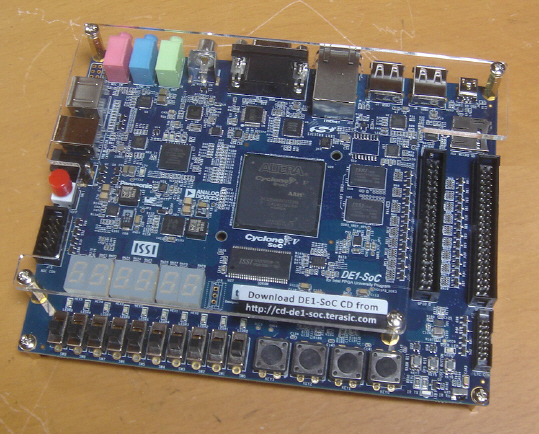

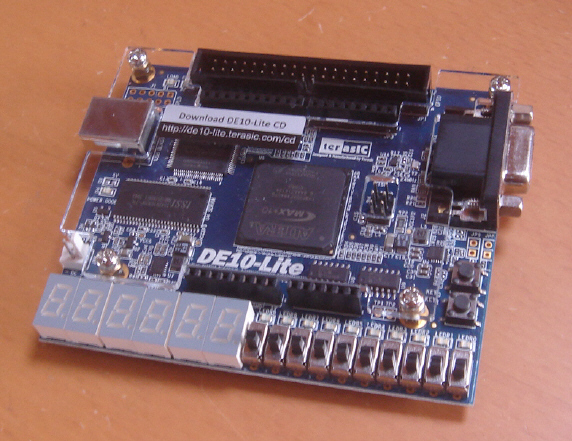

最後にHDLをDE1-SoCまたはDE10-Lite(*)に書き込み,MNIST画像が高速かつ正しく推論されるかをオシロスコープで確認する.さらにFPGA内部信号をロジックアナライザであたり,計算の結果・途中経過がPythonと一致することを確認する.

講師サイト(下記参照)の「第1部 全結合ニューラルネットワーク」のセミナ版(セミナではVHDLに加えてVerilog HDLも用意).

本セミナで扱うニューラルネットワークは全結合型ゆえ,畳み込み型(CNN)と比べると正解率は落ちるがシンプルな構成になる.本セミナの続きとしてCNN編,リアルタイム推論編も用意している.

(*)本セミナ(入門編)のみ受講する方はDE10-Lite(1万円前後)でも可. CNN編→リアルタイム推論編と進む予定の方はDE1-SoC(3万円前後)を推奨

※本セミナはGoogle Meetを使ったオンライン限定セミナです.

詳細は,オンライン限定セミナについてを参照ください.

ディープラーニング(全結合ニューラルネットワーク)のハードウェア化に挑戦する.特殊なIPコアや高位合成などは使わずに「力技」でHDL化する.

Pythonで書かれたMNISTという手書き数字画像データセットの「推論」プログラムを「整数化」して正解率がどの程度落ちるか確認する.その後重み係数や画像データをExcelに貼り付け,結果・途中経過がPythonと一致することを確認する.

その後は回路図を描き,タイムチャートでその動作を吟味した後,回路をHDL化する.その後論理シミュレーションを行い,結果・途中経過がExcelとピタリ一致することを確認する.さらに並列化,パイプライン化によって高速化する(サイクル数1/40以下).

最後にHDLをDE1-SoCまたはDE10-Lite(*)に書き込み,MNIST画像が高速かつ正しく推論されるかをオシロスコープで確認する.さらにFPGA内部信号をロジックアナライザであたり,計算の結果・途中経過がPythonと一致することを確認する.

講師サイト(下記参照)の「第1部 全結合ニューラルネットワーク」のセミナ版(セミナではVHDLに加えてVerilog HDLも用意).

本セミナで扱うニューラルネットワークは全結合型ゆえ,畳み込み型(CNN)と比べると正解率は落ちるがシンプルな構成になる.本セミナの続きとしてCNN編,リアルタイム推論編も用意している.

(*)本セミナ(入門編)のみ受講する方はDE10-Lite(1万円前後)でも可. CNN編→リアルタイム推論編と進む予定の方はDE1-SoC(3万円前後)を推奨

●対象聴講者

・電気製品にディープラーニングを組み込みたい人

・ディープラーニングを高速化,低消費電力化したい人

・FPGAに興味がある人

・PythonやC言語で書かれたアルゴリズムをHDL化したい人

講師サイトに目を通しおくとベター

●講演の目標

・大量な積和演算を必要とするアルゴリズムを実装する際,CPUやGPUの他に「FPGA」という選択肢が一つ増える

・並列化,パイプライン化ができるのでCPUより高速化が可能であり,GPUと比べて低消費電力になる

・PythonやC言語で書かれたアルゴリズムをハードウェア化する手順が分かる

・回路のどの部分を「並列化」すれば高速化できるかの勘所が分かる

・「パイプライン化」のイメージとその効果をつかめる

・特殊なIP,ライブラリ,高位合成ツールを使わず,FPGAベンダ・デバイスに依存しないHDLを作成する

●内容

1 Pythonでディープラーニング(推論)

1.1 まずは普通にPythonで実行して正解率を確認

1.2 重み係数や画像データを整数化して正解率を確認

1.3 Pythonから重み係数や画像データをファイルに書き出し

2 Excel(LibreOffice)で実行

2.1 重み係数や画像データをExcel(LibreOffice)に貼り付け

2.2 Excel(LibreOffice)の結果がPythonとピタリ一致するのを確認

2.3 Excel(LibreOffice)+VBAで重み係数のVHDL/Verilog HDLを自動生成

3 回路図とタイムチャートの説明

3.1 ROMの読み出し回路とタイムチャート

3.2 積和演算の回路とタイムチャート

3.3 擬似シグモイド関数の回路とタイムチャート

4 VHDLの説明(Verilogも用意する)

4.1 VHDLファイルの階層構造

4.2 ROMの読み出し部のVHDL

4.3 積和演算部のVHDL

4.4 擬似シグモイド関数のVHDL

5 論理シミュレーション(ModelSim)

5.1 なぜ論理シミュレーションするのか

5.2 論理シミュレーションの手順

5.3 論理シミュレーションの結果がExcelとピタリ一致するのを確認

6. 並列化とパイプライン化

6.1 1層目を並列化で高速化.サイクル数の確認・検討

6.2 2層目を並列化で高速化.サイクル数の確認・検討

6.3 パイプライン化.サイクル数の確認

7. FPGAに書いて実行

7.1 FPGAにプログラミングするまでの手順

7.2 MNIST画像が高速かつ正しく推論されるかをオシロスコープで確認

7.3 FPGA内部信号がPythonと一致することをロジックアナライザで確認

●講演の参考文献,参考URL

1. 講師サイト:http://digitalfilter.com/deeponhw/deeponhw01.html

2. ゼロから作るDeep Learning,オライリー.

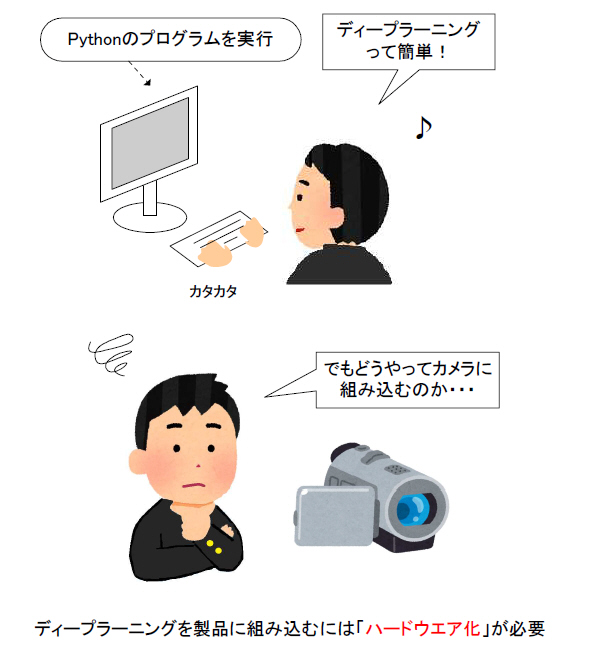

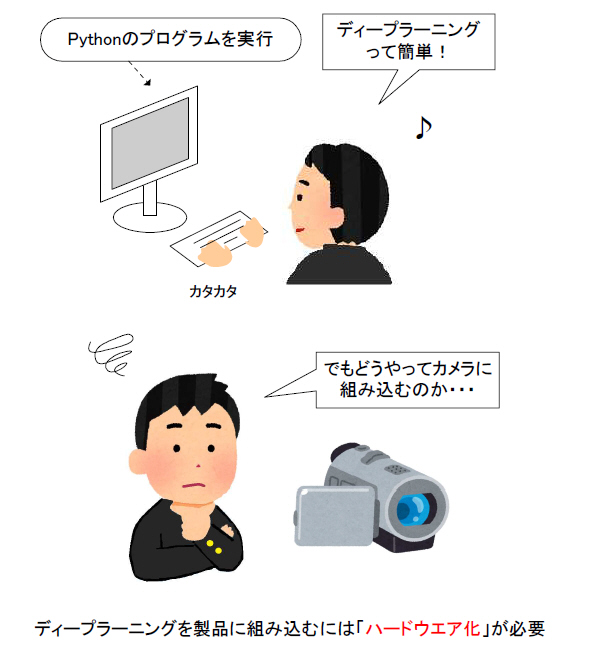

ハードウェア化が必要な理由

本セミナ全体の流れ

CNN編→リアルタイム推論編と進む予定の方は DE1-SoC(3万円前後)を推奨

本セミナ(入門編)のみ受講する方はDE10-Lite(1万円前後)でも可

クロック周期10ns x 1.1kサイクル = 11usでMNIST画像1枚認識することを確認

FPGAの内部信号をロジアナであたってPythonで計算した値とピタリ一致することを確認

・電気製品にディープラーニングを組み込みたい人

・ディープラーニングを高速化,低消費電力化したい人

・FPGAに興味がある人

・PythonやC言語で書かれたアルゴリズムをHDL化したい人

講師サイトに目を通しおくとベター

●講演の目標

・大量な積和演算を必要とするアルゴリズムを実装する際,CPUやGPUの他に「FPGA」という選択肢が一つ増える

・並列化,パイプライン化ができるのでCPUより高速化が可能であり,GPUと比べて低消費電力になる

・PythonやC言語で書かれたアルゴリズムをハードウェア化する手順が分かる

・回路のどの部分を「並列化」すれば高速化できるかの勘所が分かる

・「パイプライン化」のイメージとその効果をつかめる

・特殊なIP,ライブラリ,高位合成ツールを使わず,FPGAベンダ・デバイスに依存しないHDLを作成する

●内容

1 Pythonでディープラーニング(推論)

1.1 まずは普通にPythonで実行して正解率を確認

1.2 重み係数や画像データを整数化して正解率を確認

1.3 Pythonから重み係数や画像データをファイルに書き出し

2 Excel(LibreOffice)で実行

2.1 重み係数や画像データをExcel(LibreOffice)に貼り付け

2.2 Excel(LibreOffice)の結果がPythonとピタリ一致するのを確認

2.3 Excel(LibreOffice)+VBAで重み係数のVHDL/Verilog HDLを自動生成

3 回路図とタイムチャートの説明

3.1 ROMの読み出し回路とタイムチャート

3.2 積和演算の回路とタイムチャート

3.3 擬似シグモイド関数の回路とタイムチャート

4 VHDLの説明(Verilogも用意する)

4.1 VHDLファイルの階層構造

4.2 ROMの読み出し部のVHDL

4.3 積和演算部のVHDL

4.4 擬似シグモイド関数のVHDL

5 論理シミュレーション(ModelSim)

5.1 なぜ論理シミュレーションするのか

5.2 論理シミュレーションの手順

5.3 論理シミュレーションの結果がExcelとピタリ一致するのを確認

6. 並列化とパイプライン化

6.1 1層目を並列化で高速化.サイクル数の確認・検討

6.2 2層目を並列化で高速化.サイクル数の確認・検討

6.3 パイプライン化.サイクル数の確認

7. FPGAに書いて実行

7.1 FPGAにプログラミングするまでの手順

7.2 MNIST画像が高速かつ正しく推論されるかをオシロスコープで確認

7.3 FPGA内部信号がPythonと一致することをロジックアナライザで確認

●講演の参考文献,参考URL

1. 講師サイト:http://digitalfilter.com/deeponhw/deeponhw01.html

2. ゼロから作るDeep Learning,オライリー.

ハードウェア化が必要な理由

本セミナ全体の流れ

CNN編→リアルタイム推論編と進む予定の方は DE1-SoC(3万円前後)を推奨

本セミナ(入門編)のみ受講する方はDE10-Lite(1万円前後)でも可

クロック周期10ns x 1.1kサイクル = 11usでMNIST画像1枚認識することを確認

FPGAの内部信号をロジアナであたってPythonで計算した値とピタリ一致することを確認

【受講者が持参するもの】

オンライン限定で基本的に実習なしだが,PC(OS:Windows 7以降,64bit)に下記ソフトウェアをインストールして「予習」しておくと理解の助けになる.

・Anaconda(セミナではJupyter Labを使用)

・ExcelまたはLibreOffice

オンライン限定で基本的に実習なしだが,PC(OS:Windows 7以降,64bit)に下記ソフトウェアをインストールして「予習」しておくと理解の助けになる.

・Anaconda(セミナではJupyter Labを使用)

・ExcelまたはLibreOffice

【講師】

岩田 利王 氏〔株式会社 デジタルフィルター 代表取締役〕

音声・画像などのデジタル信号処理システム,VHDL/VerilogによるFPGA(Xilinx, Intel),dsPIC, ARM Cortex,MSP430等マイコンシステム,ラズベリーパイ,Arduino,Windowsアプリケーション,スマートフォンアプリ(Android/iPhone),プリント基板などの開発に従事.「実践ディジタル・フィルタ設計入門」,「dsPIC基板で始めるディジタル信号 処理」,「FPGAスタータ・キットで初体験!オリジナル・マイコン作り」,「FPGAパソコンZYBOで作るLinux I/Oミニコンピュータ」などCQ出版社から著書多数 .

講師サイト:http://digitalfilter.com/

岩田 利王 氏〔株式会社 デジタルフィルター 代表取締役〕

音声・画像などのデジタル信号処理システム,VHDL/VerilogによるFPGA(Xilinx, Intel),dsPIC, ARM Cortex,MSP430等マイコンシステム,ラズベリーパイ,Arduino,Windowsアプリケーション,スマートフォンアプリ(Android/iPhone),プリント基板などの開発に従事.「実践ディジタル・フィルタ設計入門」,「dsPIC基板で始めるディジタル信号 処理」,「FPGAスタータ・キットで初体験!オリジナル・マイコン作り」,「FPGAパソコンZYBOで作るLinux I/Oミニコンピュータ」などCQ出版社から著書多数 .

講師サイト:http://digitalfilter.com/