1章 FPGAとFPGAの開発環境

1.1 FPGA(Field-Programmable Gate Array)とは?

1.2 FPGAの回路(設計)情報 =コンフィグレーション

演習1:FPGA 開発環境 Quartus Prime Lite

2章 HDLによって回路を記述する

2.1 回路図とHDL(Hardware Description Language)ソフトウエアの違い

2.2 VHDLの基本的な書式

2.3 HDLシミュレータとテストベンチ

演習2:HDLシミュレータ ModelSim

3章 ソフトウエア・ラジオで使われる信号処理回路

3.1 発振器:NCO(Numerically Controlled Oscillator)

演習3:NCOで作る低周波発振器

3.2 周波数変換器:ミキサ/乗算器

3.3 フィルタ(1):CIC(Cascaded Integrator-Comb)フィルタ

演習4: CICフィルタの設計

3.4 フィルタ(3):FIR(Finite Impulse Response)フィルタ

演習5(*): 受信帯域フィルタの周波数特性の測定

3.5 CORDIC(Coordinate Rotational Digital Computer)とその用法

4章 性能を極めるための重要な脇役:アナログ回路

4.1 アンチ・エイリアシング(Anti-Aliasing)フィルタの特性

4.2 プリアンプに要求される雑音指数と増幅度

4.3 クロックの位相雑音

5章 高性能FMレシーバの実装

5.1 適応フィルタによるマルチパス・キャンセラ

演習6(*):信号発生器による感度(SN比)の測定

演習7:屋外のアンテナを接続してマルチパス・キャンセラを運転

5.2 パイロット・トーン方式 FMステレオ伝送の詳細

演習8(*):信号発生器によるチャンネル・セパレーションの測定

(*):講師によるデモンストレーション・実演でご紹介します.

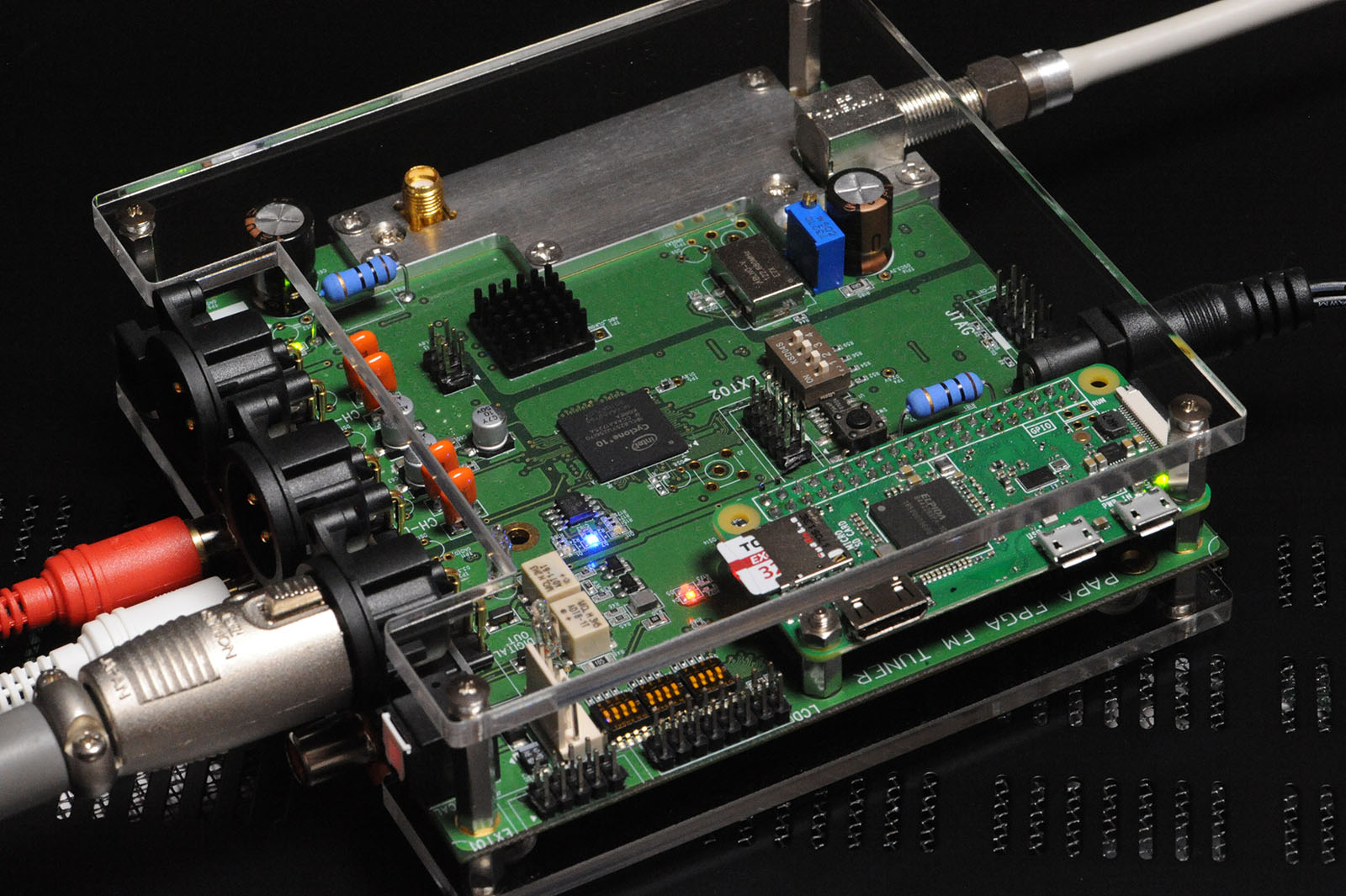

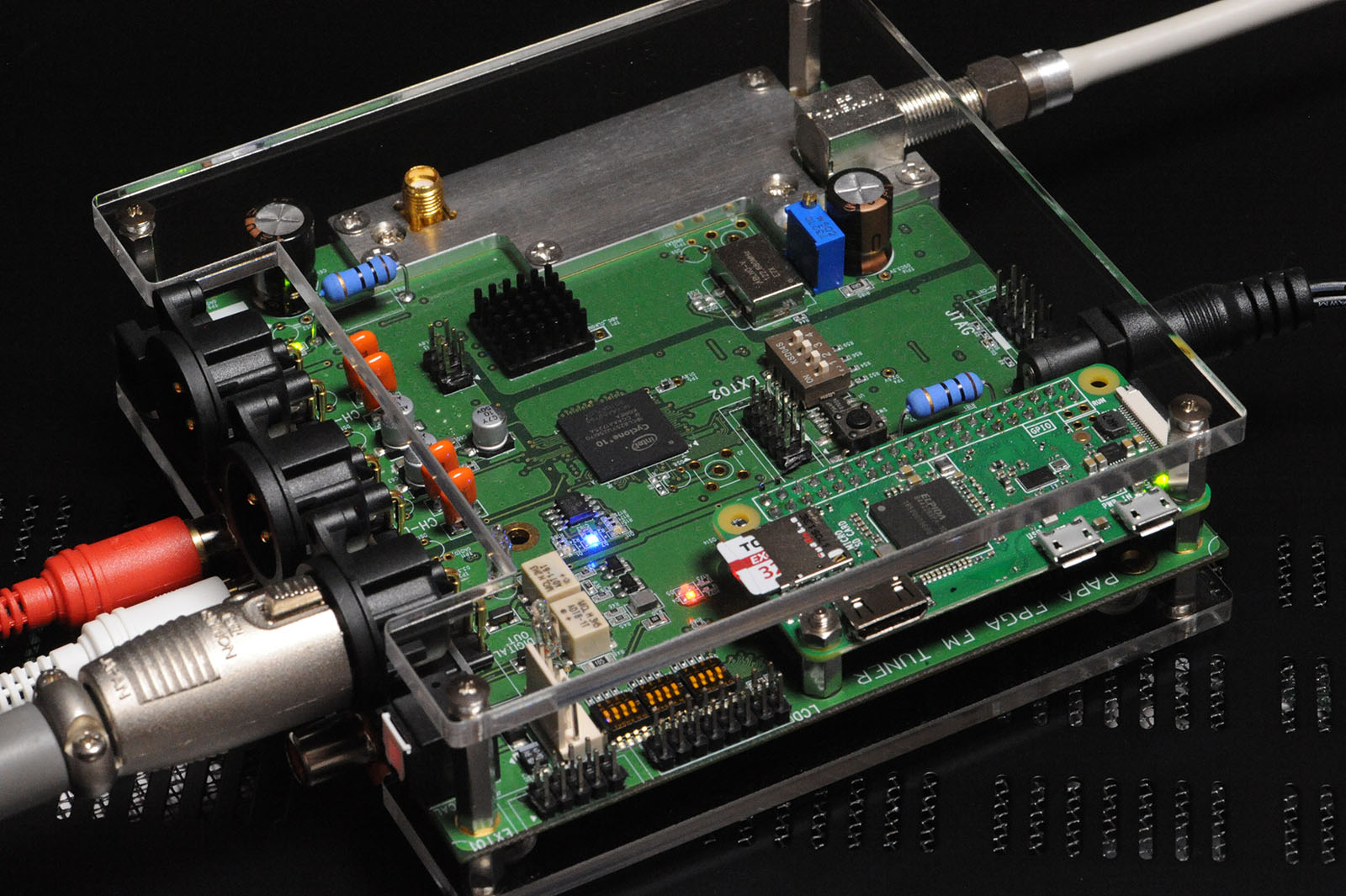

FMレシーバ・サンプル画像1

FMレシーバ・サンプル画像1 FMレシーバ・サンプル画像2●対象聴講者

FMレシーバ・サンプル画像2●対象聴講者

・ソフトウエア・ラジオに興味があり,そこで使われている信号処理について学びたい方

・アナログ方式の受信機,回路については詳しいが,ディジタル信号処理は敷居が高いと感じていて手を出しかねている方

・FPGAを今後,信号処理のために使っていきたいと考えている方

・高音質のFMチューナをその内部の動作を理解した上で使いたい方

●講演の目標

・ソフトウエア・ラジオで使われている信号処理について理解を深める

・信号処理の目的のため、FPGAを実際の機器の中で使い始めることができる

・通信機の性能を高める、いくつかの基本的なアプローチを習得する