1. Pythonでディープラーニング(推論)の実習

1.1 まずは普通にPythonで実行して正解率を確認

1.2 重み係数や画像データを整数化して正解率を確認

1.3 Pythonから重み係数や画像データをファイルに書き出し

2. Excel(LibreOffice)でディープラーニングの実習

2.1 重み係数や画像データをExcel(LibreOffice)に貼り付け

2.2 Excel(LibreOffice)の結果がPythonとピタリ一致するのを確認

2.3 Excel(LibreOffice)+VBAで重み係数のVHDL/Verilog HDLを自動生成

↑以上まで実習。↓以下座学になります。

3. 回路図とタイムチャートの説明

3.1 ROMの読み出し回路とタイムチャート

3.2 積和演算の回路とタイムチャート

3.3 擬似シグモイド関数の回路とタイムチャート

4. VHDLの説明(Verilogも用意する)

4.1 VHDLファイルの階層構造

4.2 ROMの読み出し部のVHDL

4.3 積和演算部のVHDL

4.4 擬似シグモイド関数のVHDL

5. 論理シミュレーション(ModelSim)

5.1 なぜ論理シミュレーションするのか

5.2 論理シミュレーションの手順

5.3 論理シミュレーションの結果がExcelとピタリ一致するのを確認

6. 並列化とパイプライン化

6.1 1層目を並列化で高速化。サイクル数の確認・検討

6.2 2層目を並列化で高速化。サイクル数の確認・検討

6.3 パイプライン化。サイクル数の確認

7. FPGAに書いて実行

7.1 FPGAにプログラミングするまでの手順

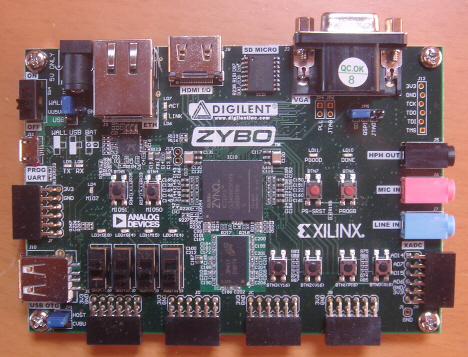

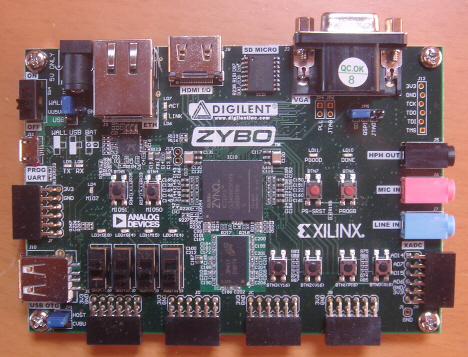

7.2 SDカードイメージをコピーしてZYBOで実行

8. 畳み込みニューラルネットワークのハードウェア化の紹介

8.1 全結合に比べて畳み込みはより大量の積和演算が必要

8.2 ビットシフト演算で乗算器を節約する

ハードウェア化が必要な理由

ハードウェア化が必要な理由

本セミナ全体の流れ

本セミナ全体の流れ

HDL化の部分の流れ

HDL化の部分の流れ

ZYBO Zynq7000に実装する●対象聴講者

ZYBO Zynq7000に実装する●対象聴講者

・電気製品にディープラーニングを組み込みたい人

・ディープラーニングを高速化、低消費電力化したい人

・FPGAに興味がある人

・PythonやC言語で書かれたアルゴリズムをHDL化したい人

下記講師サイトに目を通しおくとベター

●講演の目標

・大量な積和演算を必要とするアルゴリズムを実装する際、CPUやGPUの他に「FPGA」という選択肢が一つ増える

・並列化、パイプライン化ができるのでCPUより高速化が可能であり、GPUと比べて低消費電力になる

・PythonやC言語で書かれたアルゴリズムをハードウェア化する手順が分かる

・回路のどの部分を「並列化」すれば高速化できるかの勘所が分かる

・「パイプライン化」のイメージとその効果をつかめる

・本セミナではHLS(High Level Synthesis、高位合成)ツールは使わないが、本セミナの勘所と、HLSのそれとは共通点が多い

●講演の参考文献、参考URL

1. 講師サイト:http://digitalfilter.com/deeponhw/deeponhw01.html

2.

ゼロから作るDeep Learning、オライリー。

3.

FPGAパソコンZYBOで作るLinux I/Oミニコンピュータ、CQ出版社。