●対象聴講者

・FPGAでオーディオ(音声)の信号処理をしたい方

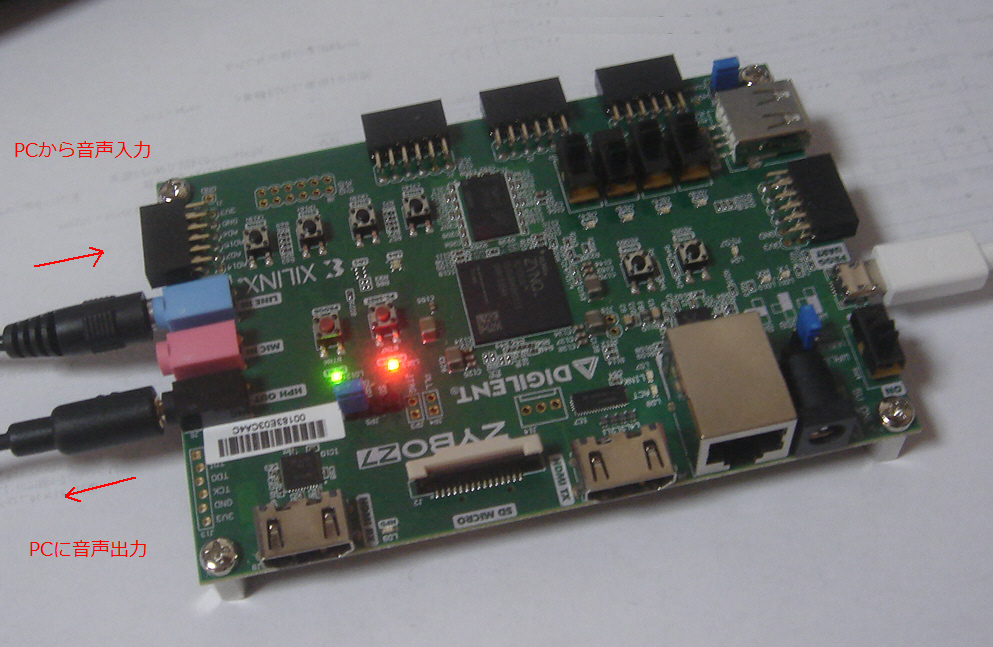

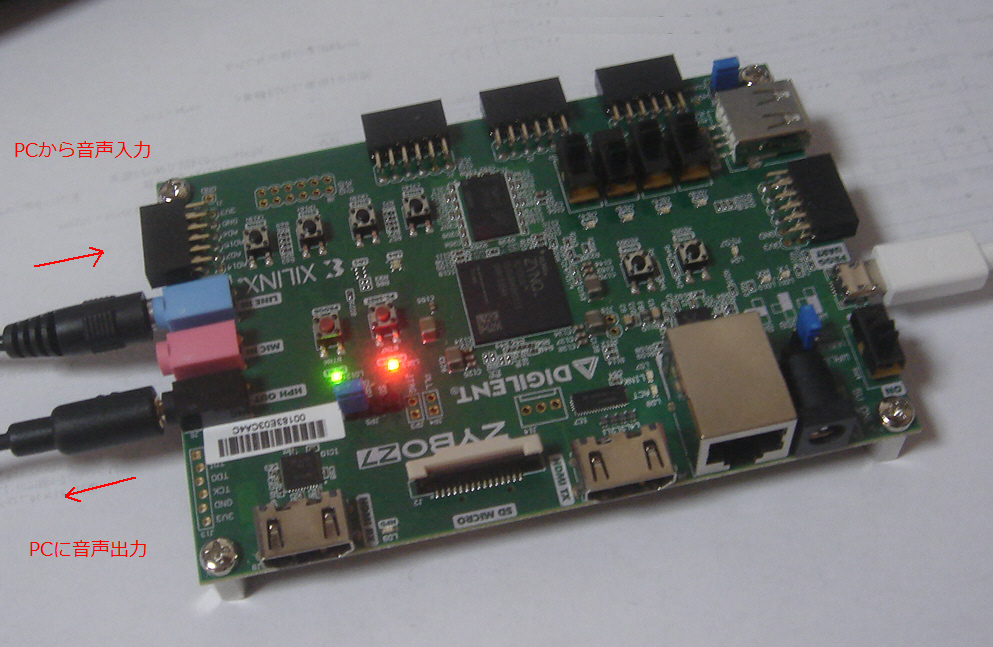

・Zyboを持っている方(7000,Z7-10,Z7-20どれでも可,下の写真参照)

・パソコンでFPGA開発から入出力波形の確認までしたい方(Windows/Linuxどちらも可)

・Vitisを使いたくない方(Vivadoだけをインストールして使いたい)

・ARMやMicroBlazeのようなFPGA内蔵マイコンを使いたくない方(ロジックのみで開発)

・Verilogのみ,またはVHDLのみで開発したい方(両言語を用意する予定)

・I2CをHDL化したい方(マイコンではなくロジックでシリアル通信したい)

・ディジタル・フィルタを多チャネル化,多段化したい方

・FPGA内部のRAM/ROMを使って高次のFIRフィルタを構成したい方

・FPGA実装前に論理シミュレーションでデバッグしたい方

・FPGA実装後にロジック・アナライザでデバッグしたい方

●講演の特徴と目標

・Zybo(7000,Z7-10,Z7-20)にディジタル・フィルタを実装できる

・ツールはVivadoのみでOK(Vitisは必要ない)

・パソコンはWindowsでもLinuxでもOK

・ARMやMicroblazeといったプロセッサは使わない

・ベンダフリーなHDL(他社FPGAに移植も容易)

・VerilogとVHDL両方用意する予定

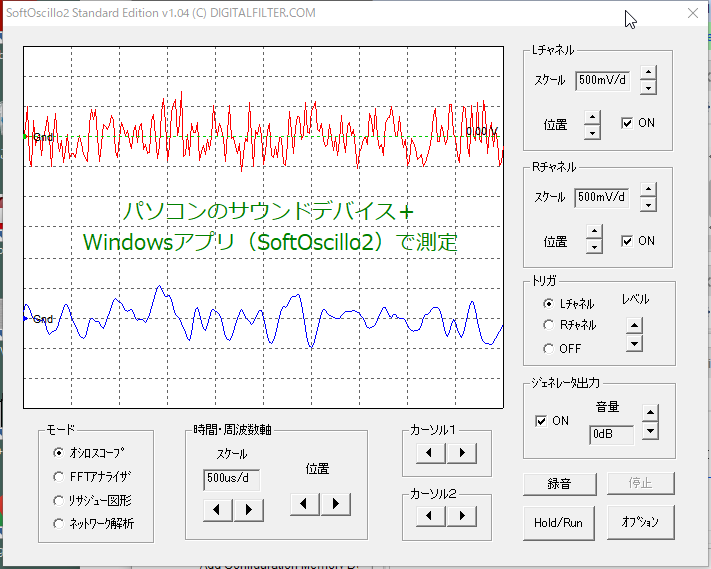

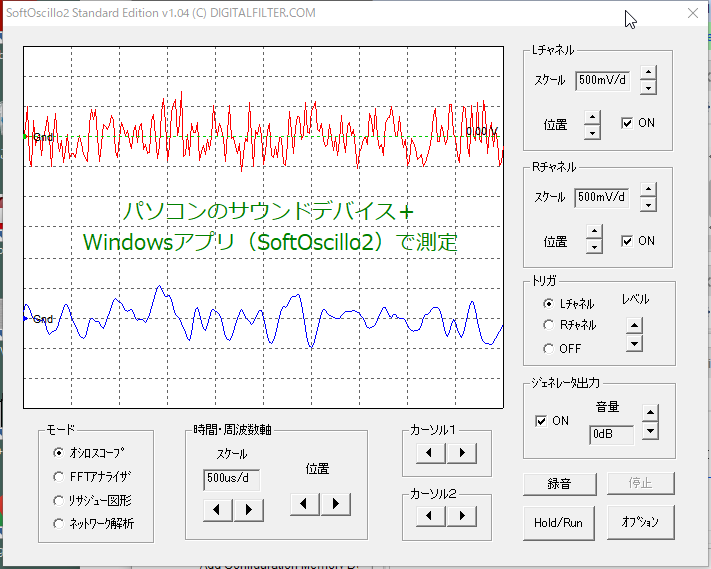

・パソコンのサウンド・デバイスでフィルタ入出力を測定

・FIR/IIR型フィルタのHDLが分かる

・IIC通信(SSM2603設定用)のHDLが分かる

・音声の信号処理ができる

・フィルタ係数導出法が分かる

・FPGAの強みである並列性,リアルタイム性を実感できる

・メモリ・アクセスと積和演算が中心で応用範囲が広い(AIなど)

●内容

1 Vivadoプロジェクトの作成

ボード(Zybo Z7-020など)の選択

デザイン用HDLファイルを追加

コンパイル(論理合成)が成功することを確認

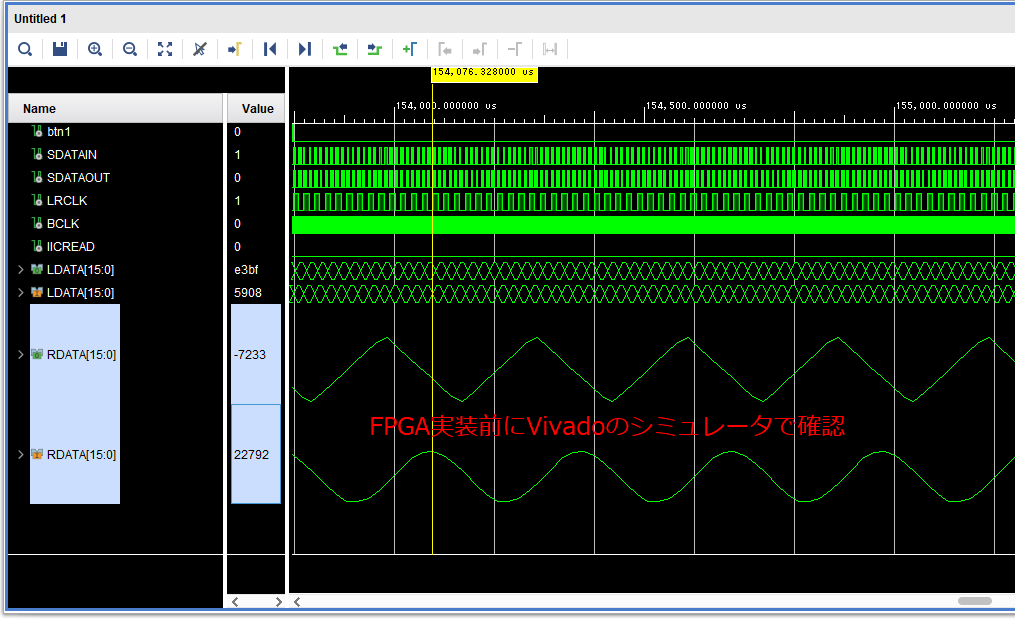

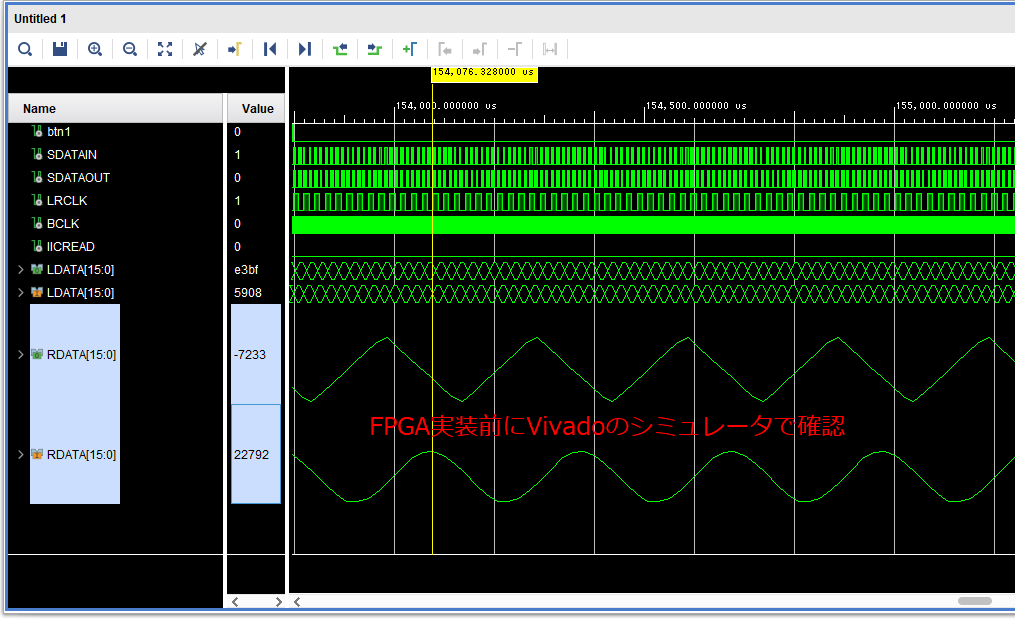

2 Vivadoで論理シミュレーション(下記URL①)

シミュレーション用HDLファイルを追加

I2C(IIC)通信をシミュレーションで確認

SSM2603(オーディオ・コーデック)の入出力を見る

S-P(シリアル-パラレル),P-S(パラレル-シリアル)変換回路を見る

フィルタの入出力(Low Pass特性)を見る

3 VivadoからFPGAをプログラム(下記URL②)

Clocking Wizardでクロック生成(44.1kHz*256)

ピン・アサイン(どの入出力がどのピンに行くか決める)

コンパイル→ビット・ストリーム生成

フィルタをFPGAにプログラム

フィルタ出力の音を聞いてLow Pass特性を実感

サウンド・デバイス+SoftOscillo2(Windowsアプリ)で測定

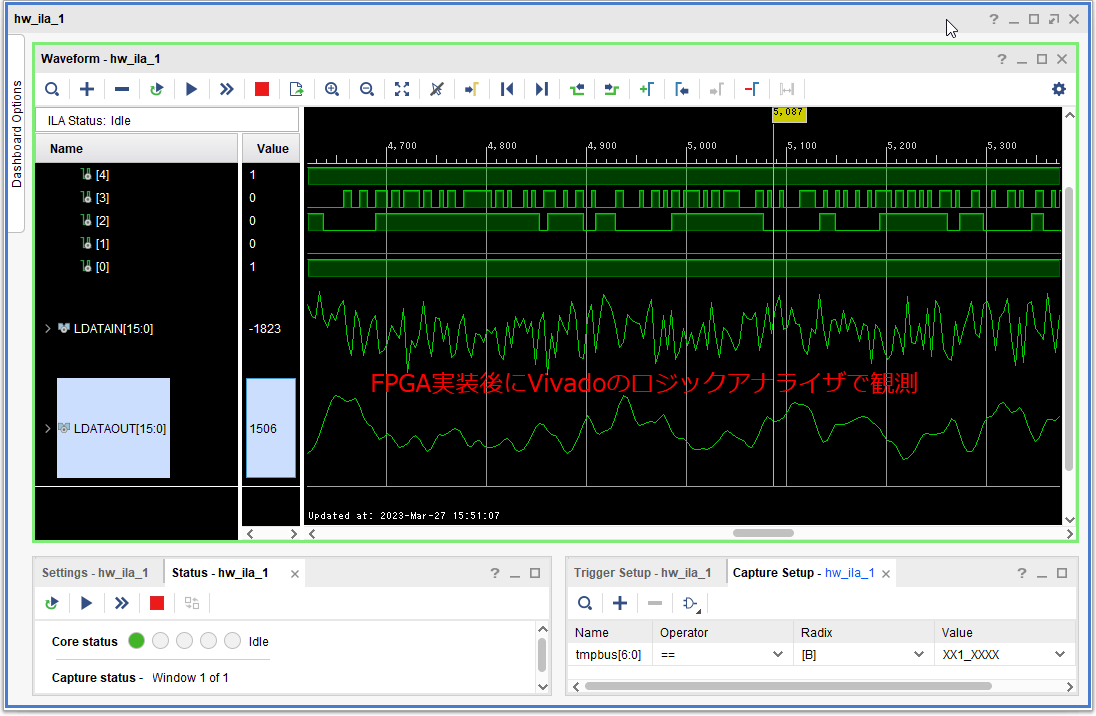

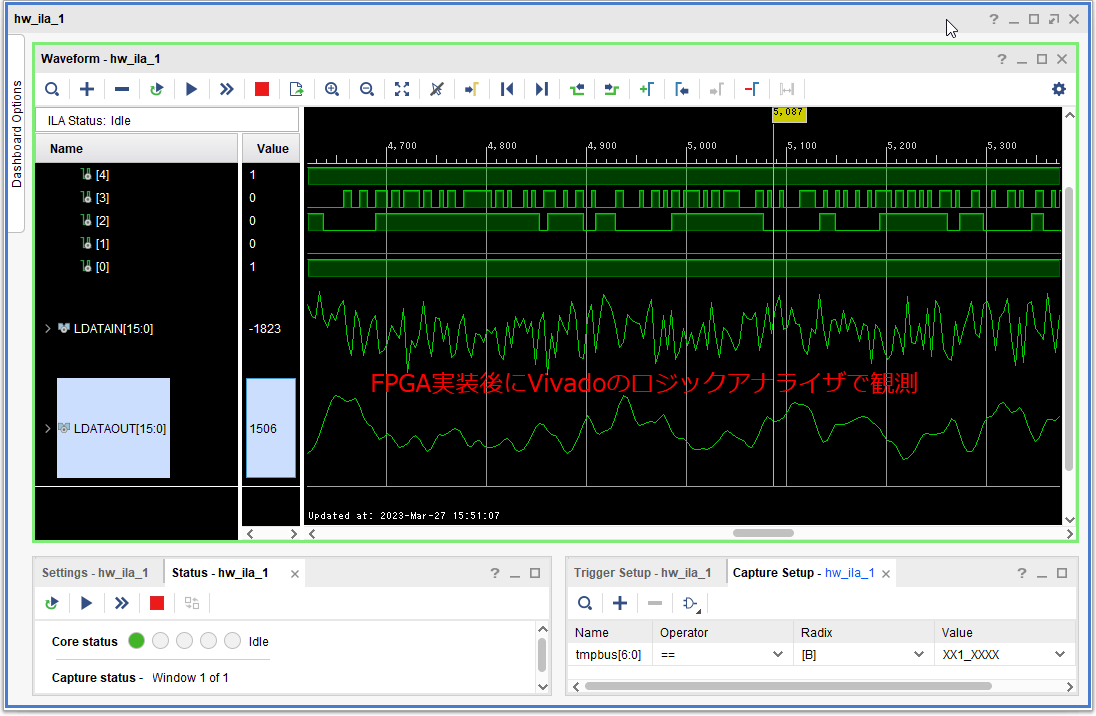

4 Vivadoのロジック・アナライザで内部信号を見る(下記URL③)

ILA(Integrated Logic Analyzer)を追加

ILAに信号やクロックを登録

トリガ設定で見たい瞬間の波形を取り込む

キャプチャ設定で効率よく波形を取り込む

I2C通信,SSM2603の入出力をロジアナで観測

S-P,P-S,フィルタ回路の入出力を観測

5. DSPLinksで係数導出

フィルタ設計用Windowsアプリ-DSPLinks

パラメータの設定

周波数特性を見る

フィルタ係数を整数化する

IIR/FIRフィルタの係数を変えてプログラム→測定

6. IIR/FIRフィルタ回路の説明

ブロック図,差分方程式,伝達関数,回路図

回路図をHDLで表現する

IIRのHDLの注意点(係数の極性,縦続接続の勘所等)

FIRのHDLの注意点(RAMにデータ,ROMに係数,それらの記述等)

積和演算のタイム・チャート(シミュレータ,ロジアナとの比較)

シミュレーション用HDLの説明

7. フィルタ以外の回路の説明

S-P/P-S,I2C通信,チャタリング・ノイズ対策回路の説明

●参考動画

1 ZYBO Z7-20でデジタル信号処理(3)

ZYBO Z7-20でデジタル信号処理(3)

2 ZYBO Z7-20でデジタル信号処理(4)

ZYBO Z7-20でデジタル信号処理(4)

3 ZYBO Z7-20でデジタル信号処理(5)

ZYBO Z7-20でデジタル信号処理(5)

使えるZyboはこの3種類(7000,Z7-10,Z7-20)

使えるZyboはこの3種類(7000,Z7-10,Z7-20)

パソコン1台あれば実験ができる(音声信号を入出力)

パソコン1台あれば実験ができる(音声信号を入出力)

FPGA実装前に論理シミュレーションする

FPGA実装前に論理シミュレーションする

FPGA実装後はロジック・アナライザでデバッグ

FPGA実装後はロジック・アナライザでデバッグ

フィルタの出力をWindowsアプリ(SoftOscillo2)で測定

フィルタの出力をWindowsアプリ(SoftOscillo2)で測定