メモリからのデータの取り出し/外部デバイスへの出力処理はビデオ・システムに限らずあらゆるシステム開発で必須となる技法だが,その原理は何となくわかっていても,DMA処理やタイミング信号生成処理など,いざ実システムで具現化しようとすると意外とわかりにくく,その作成に手がかかる部分である.

他方,最近では高位合成ツール(HLS)の発展により,バス動作原理など低位の基礎技術に関して深い知識がなくても,ハードウェア・ロジック設計が可能になってきた.

本講座ではXilinx社製Zynqデバイスを搭載したDigilent社製FPGAボードZyboとその設計ソフトウェアVivado2017.4,そしてAptina社製イメージセンサ・モジュールを使用して,高位合成とブロック・デザイン手法をとりいれた'非'HDL設計で実際に外部デバイス(イメージャ・モジュール)からのイメージ・データをDMAでメモリへ取り込む'俺用'グラバ・コントローラ作成の実習を行い,そのポイントを習得する.

また,出来上がったデザインの資産蓄積・再利用を容易にする,IPパッケージ化手法も合せて習得する.

※ パソコンやイメージャ・モジュールなど,実習に使用する機材は事務局でご用意します.

※同講師によるセミナ

「直伝!最新FPGAを使ったビデオ・システムの開発/IP開発(ビデオ・データ出力処理編)」を同時にお申込みいただいた方は,受講費用を10%引きいたします.

1.イメージ・センサ基礎

1.1 基本知識

1.2 I2C

1.3 べイヤ配列

1.4 タイミング信号

2.メモリ・アクセス(書き込み)基礎

2.1 メモリバス・バスマスタ・バースト転送

2.2 AXIバスプロトコル

2.3 DRAM(DDRx-SDRAM)とSRAMの違い(参考)

3.開発環境概要

3.1 設計ツール

3.2 リファレンス・ボード

3.3 おすすめ参考ドキュメント

3.4 システム構成

4.システム構築準備

4.1 フレームバッファ,ラインバッファ

4.2 クロック・ドメイン交差

5.システム構築実習処理

5.0.0 グラバ・コントローラのしくみと各処理サブ・ブロック機能のレビュー

5.0.1 ベース・システムデザインのレビュー※IP開発(ビデオ・データ出力処理)編の完成デザイン

5.1 ラインカウント処理サブブロックの作成

5.2 DMA書き込み処理サブブロックの作成

5.3 アドレス生成処理サブブロックの作成

5.4 MPU制御レジスタI/F処理(ペリフェラル・バスアダプタ)サブブロックの作成

5.5 サブブロックの統合とIPパッケージ

5.6 作成したディスプレイ・コントローラIPのベース・システムデザインへの組み込み

5.7 制御ソフトウェアの作成と実機ボードでの動作確認

6.質疑応答

※進行状況により内容が一部変更となることがあります.

本セミナで使用するDigilent社製FPGAボード"ZYBO"

本セミナで使用するDigilent社製FPGAボード"ZYBO"-- http://www.avnet.co.jp/kits/Digilent/ZYBO.aspx

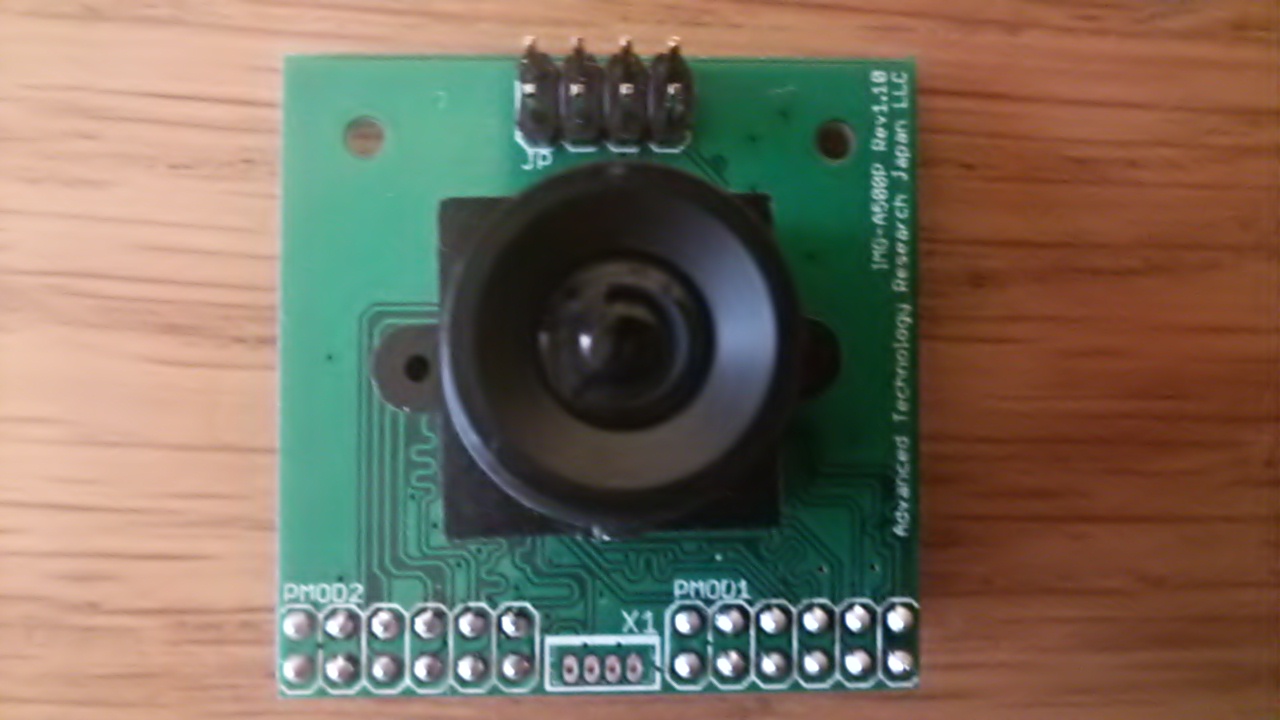

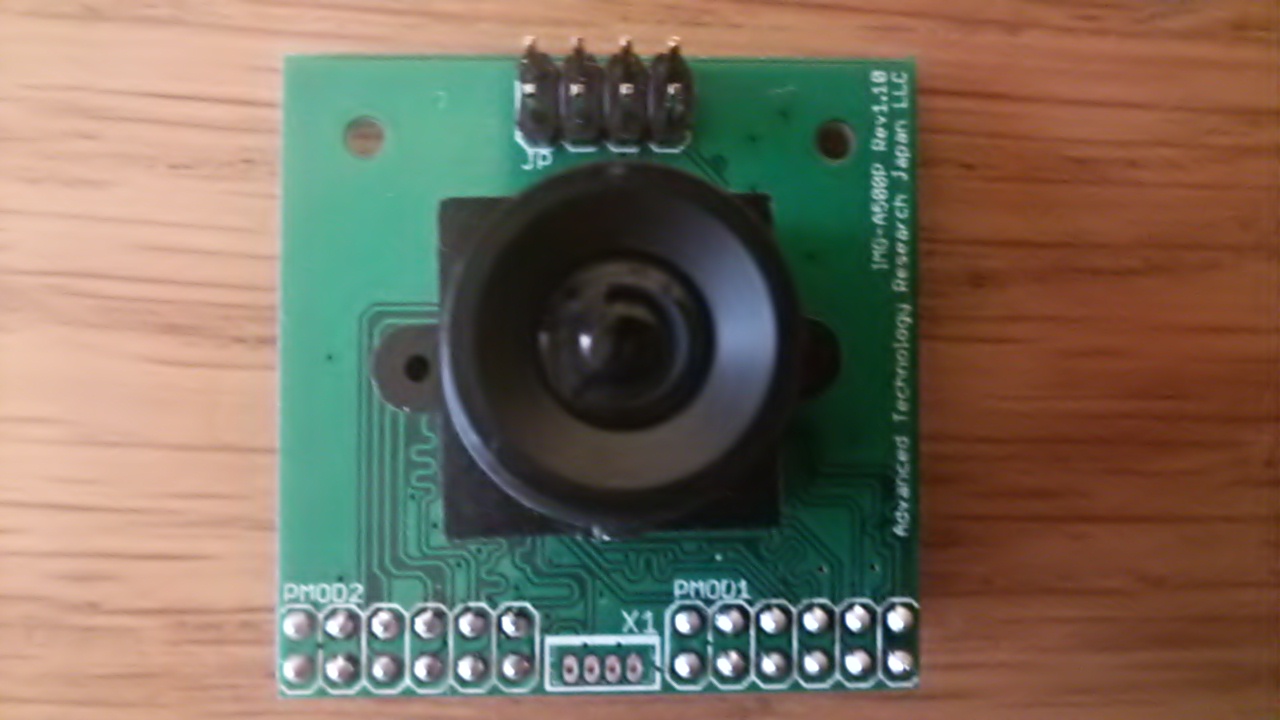

本セミナで使用するATRJ社製イメージャ・モジュール"IMG-A500P"

本セミナで使用するATRJ社製イメージャ・モジュール"IMG-A500P"-- http://www.avnet.co.jp/kits/Xilinx/IMG-A500P.aspx

セミナ受講時にZyboボードもご購入いただけるバンドル・プランもご用意しています.

受講料金込み\54,000-(税込)!※特典1.USBケーブル付属,セミナ,ボードをそれぞれ個別購入するよりもお得です.セミナお申込み時にご指定ください.

イメージャ・モジュール・オプション:通常販売価格(\20,000)より15%オフの¥17,000でご提供.ご希望の方は,お申込み時ご連絡ください.●対象聴講者

・IP開発および設計資産再利用に興味のある方

・C言語設計およびブロック設計での'脱'HDL設計に興味のある方

・低コストで高精細ビデオ・システムを開発しようとしている方

・DMA等メモリ操作手法の基礎を理解したい方

・同講師によるセミナ

「直伝!最新FPGAを使ったビデオ・システムの開発/IP開発(ビデオ・データ出力処理編)」を受講していることが望ましい

●講演の目標

・バスマスタでのメモリ・アクセス方法(取りこみ)の理解

・イメージャ基礎の理解

・IPパッケージ化とそのシステムへの組み込み・利用方法の理解

・高位合成でのバスI/F作成方法の理解

・ブロックベース設計手法の理解

●参考文献

・早乙女 勝昭 共著;『

FPGAマガジン No.10 やっぱり楽ちん!C言語×FPGA』,CQ出版社,2015年7月.

・早乙女 勝昭 共著;『

FPGAマガジン No.10 やっぱり楽ちん!C言語×FPGA【PDF版】』,CQ出版社,2015年8月.

・早乙女 勝昭 共著;『

FPGAマガジン No.6 カメラ×画像処理×FPGA』,CQ出版社,2014年7月.

・早乙女 勝昭 共著;『

FPGAマガジン No.6 カメラ×画像処理×FPGA【PDF版】』,CQ出版社,2014年8月.