MAX10はEEPROM内蔵かつ安価で非常に使いやすいFPGAで,雑誌の付録にもなったことのある人気商品である.

ロジック・エレメントは,最大50,000LEであり,マイクロプロセッサも余裕で搭載できる容量がある.そこで本講座では,FPGAを単なる論理回路の実現デバイスとして使用するのではなく,アルテラから提供されているNios IIというマイクロプロセッサを搭載し,高速な処理を論理回路,複雑な処理をマイクロプロセッサで処理する技術を学ぶ.

本講座では,基礎的な知識の確認と復習から,Verilog-HDLを使った論理回路の実験,Nios IIマイクロプロセッサの組み込みと使い方といった実用的な内容までを網羅する.

1.DE10-LiteとMAX10の概要

1.1 MAX10の特徴

1.2 DE10-Liteの特徴

1.3 DE10-Liteの拡張コネクタ

1.4 DE10-Liteの開発環境

2.論理回路とVerilog-HDL

2.1 論理回路の復習

2.1.1 ブール代数

2.1.2 論理回路(AND,OR,NOTおよびXOR)

2.1.3 組み合わせ回路

2.1.4 順序回路とフリップ・フロップ

2.1.5 ブロック図

2.2 Verilog-HDL

2.2.1 モジュールとポートリスト

2.2.2 モジュールの構成要素とモジュールの接続(assign,function,always)

2.2.3 組み合わせ回路の記述

2.2.4 順序回路の記述

2.2.5 ROM回路の記述

3.CPLDとFPGA~MAX10

3.1 CPLDによる論理回路の実現方法

3.2 FPGAによる論理回路の実現方法

3.3 CPLDとFPGAの特徴と欠点,MAX10によるアプローチ

4.Quartus Primeを使った論理回路の実験

4.1 スイッチとLEDの点灯

4.2 ROMを使った7セグメントLEDの点灯

4.3 カウンタ

4.4 デジタル時計

4.5 A-Dコンバータを使った温度計*

5.Nios II+C言語によるアプリケーション開発

5.1 Nios II gen2について

5.2 Qsysの使い方

5.3 ユーザー・モジュールの作成

5.4 Nios IIによるデジタル時計

5.5 グラフィックLCDモジュールについて

5.6 グラフィック・ライブラリ

5.7 グラフィック・ライブラリを使用したアプリケーション開発

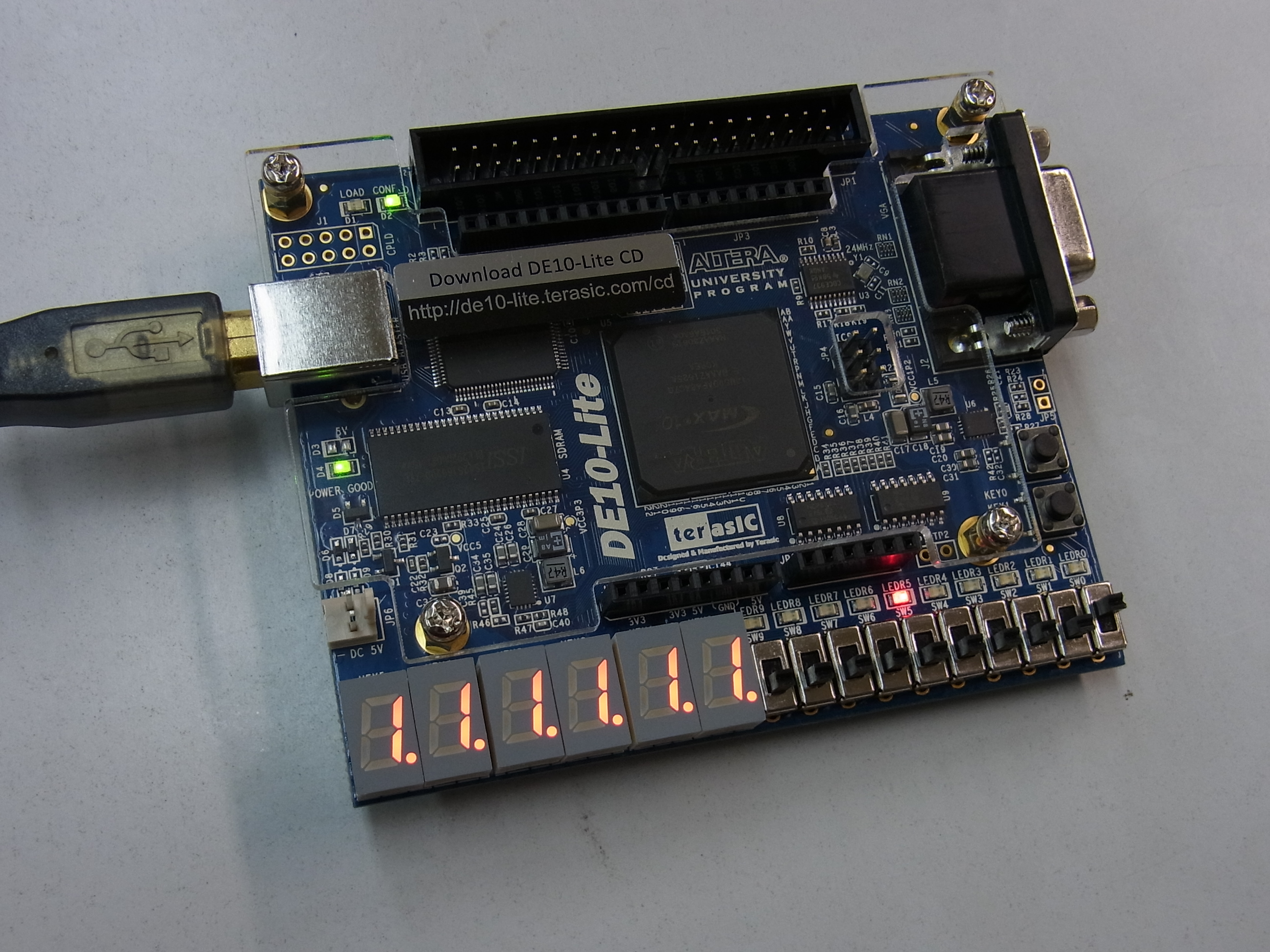

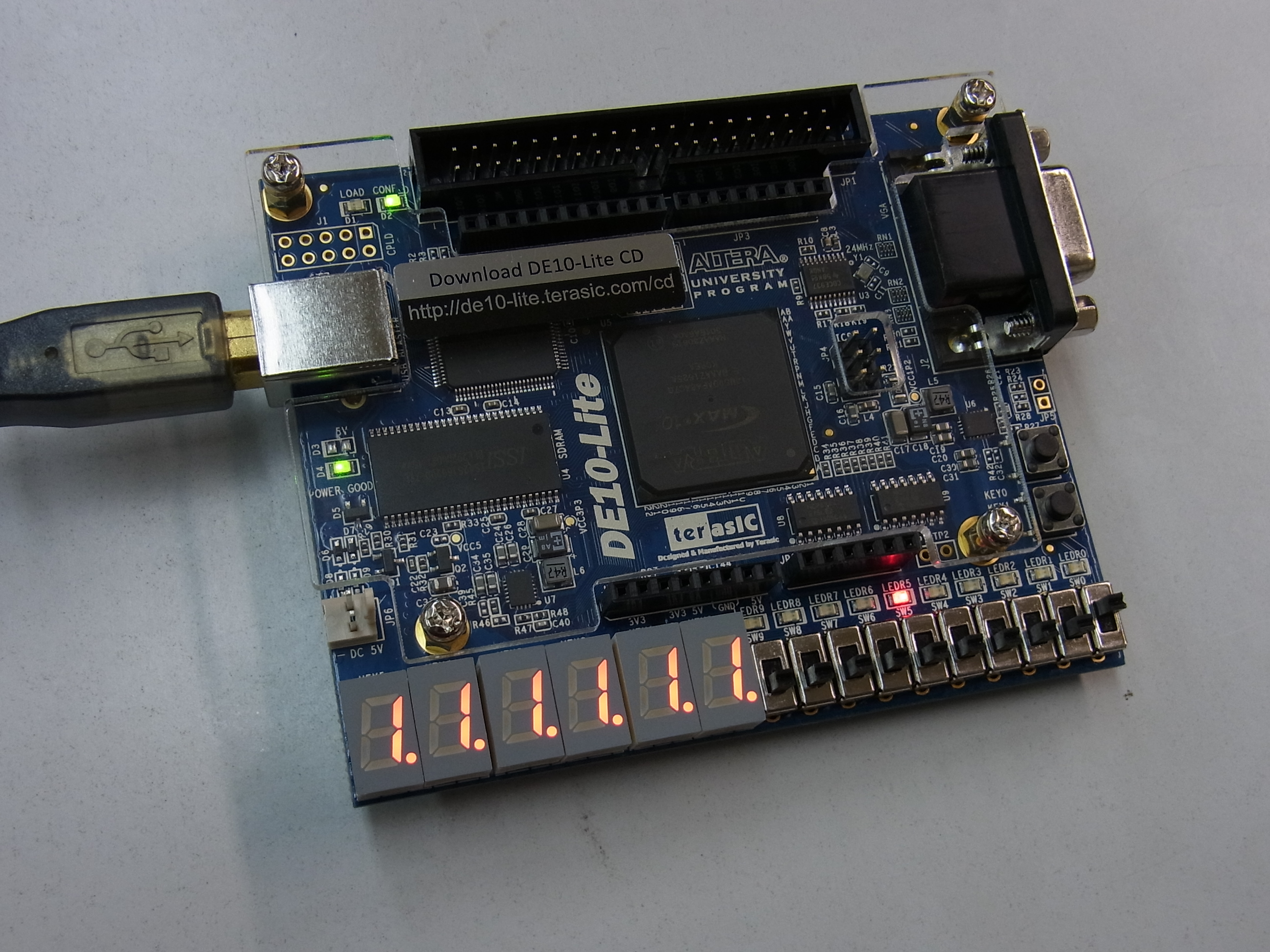

実習に使用するMAX10搭載FPGAボードDE10-Lite

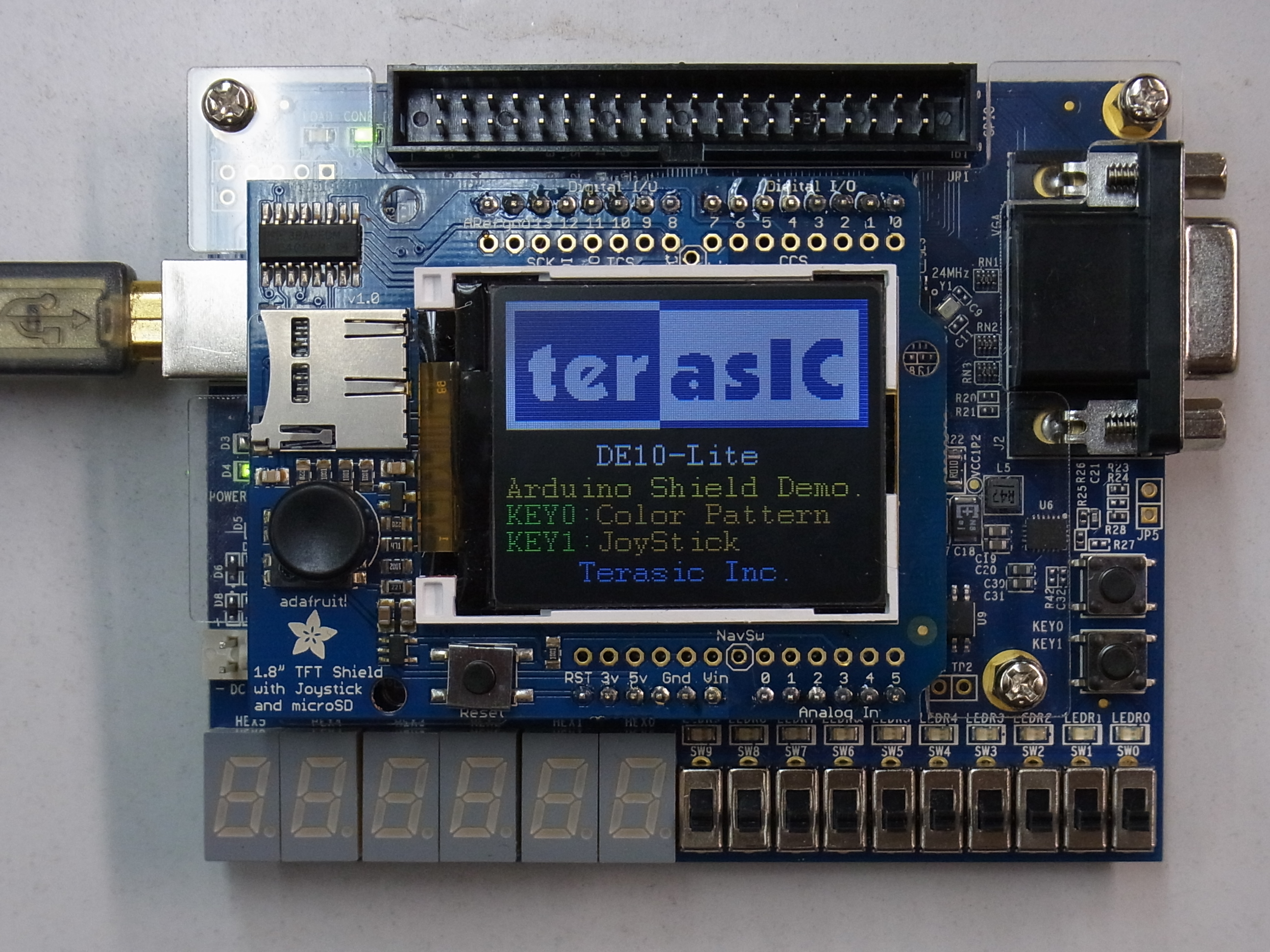

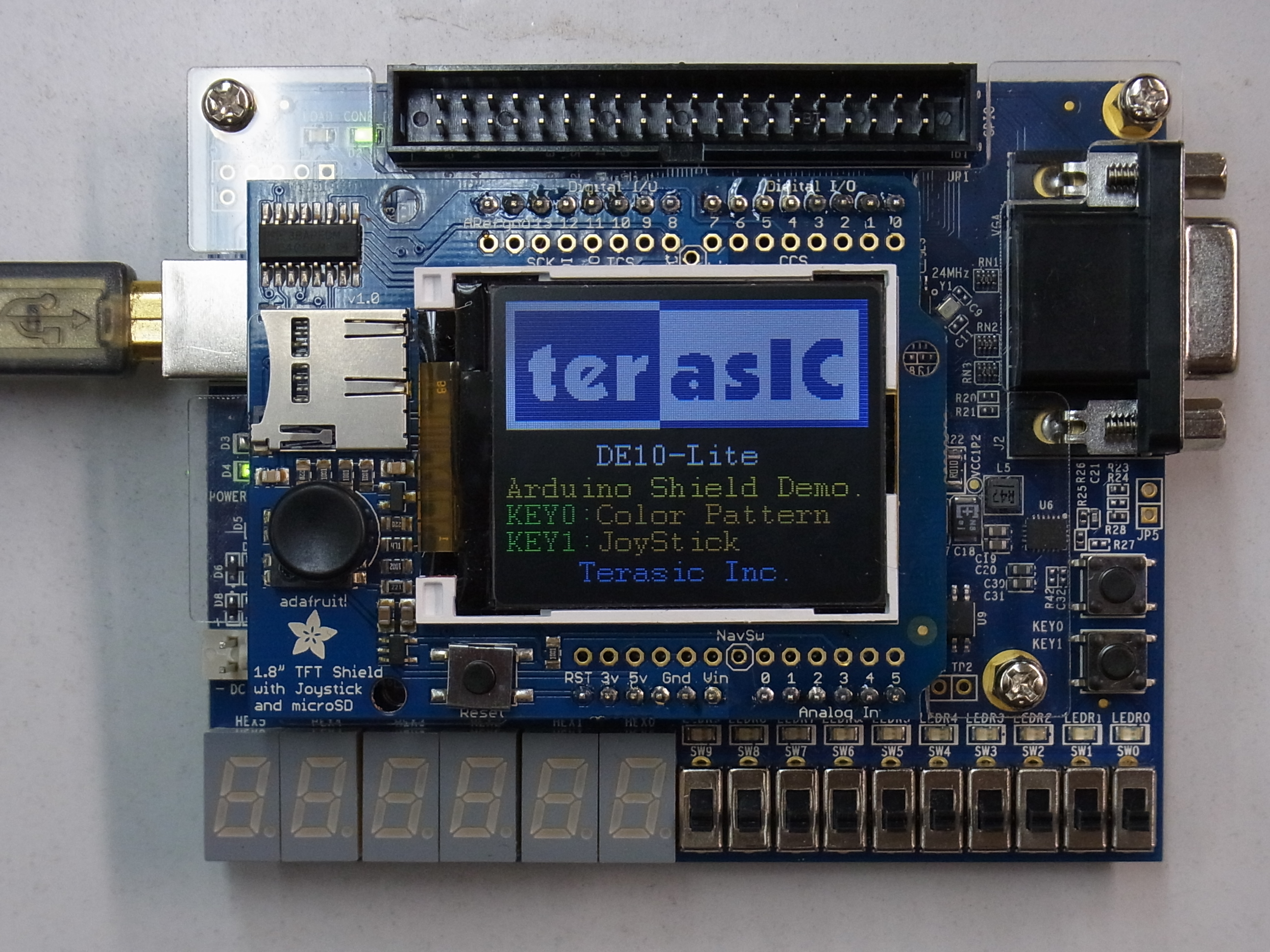

実習に使用するMAX10搭載FPGAボードDE10-Lite 拡張キットのカラー・グラフィックLCDを載せた同ボード●対象聴講者

拡張キットのカラー・グラフィックLCDを載せた同ボード●対象聴講者

・Verilog-HDLの実用的なプログラムを学びたい人

・DE10-Liteを使い込みたい人

・グラフィックLCDの制御をしてみたい人

・論理回路やVerilog-HDLの基礎は知っているが,実際のプログラムを学んでみたい人

●講演の目標

1日の講義だけで全てを習得することは難しいし,全てを説明することも難しいが,一度実際に経験しておくと,次に学んだ時に思い出して学習効果が高まり,より深く理解できるようになる.講義内容の関係で,どうしても基礎的な事項や技術的な説明が多くなるが,大事なのはFPGAやNios IIを使って何かを作ることを楽しむことだと考えている.受講者の方には,より多くの想像力を発揮し,様々な政策に挑戦して頂きたいと思う.