直伝!最新FPGAを使ったビデオ・システムの開発・外部インターフェース(カメラリンク受信)追加編

直伝!最新FPGAを使ったビデオ・システムの開発・外部インターフェース(カメラリンク受信)追加編

|

|

【開催日】2017年3月9日(木) 10:00-18:00 1日コース

【セミナNo.】ES17-0012 【受講料】29,000円(税込)

【会場】東京・巣鴨 CQ出版社セミナ・ルーム [地図]

【セミナNo.】ES17-0012 【受講料】29,000円(税込)

【会場】東京・巣鴨 CQ出版社セミナ・ルーム [地図]

近年,FPGAデバイスのめざまし発展(性能向上,大規模化,ローコスト化)により,従来ASICで行っていた複雑なシステム・オン・チップ(SoC)の実現をデスクトップ上で手軽に実現できるようになってきた.

MPU等のIP(再利用可能設計済み回路)を使用することによりハードウェア設計の深い知識がなくてもオリジナル・チップを開発することが可能である.また内部ロジック・リソースのみならず,SerDesやディレイなどI/O専用のロジックもあり高速なシリアル・データ通信も外付けチップなしで実現できる.

本講座では高性能MPUを搭載した最新FPGAで構築した簡単なカメラ・システムにカメラリンク送信I/F機能を実装して外部へのデータ送信を実現する.

※最新FPGAボードも同時に入手できるお得なバンドル・プランもあります.

※同講師によるセミナ「直伝!最新FPGAを使ったビデオ・システムの開発・外部インターフェース(カメラリンク送信)拡張編」を同時にお申込みいただいた方は,受講費用を10%引きいたします.

本セミナの終了時刻は18:00を予定しています

テキスト以外にチュートリアルに最適なサンプル・デザインをお持ち帰りいただけます

MPU等のIP(再利用可能設計済み回路)を使用することによりハードウェア設計の深い知識がなくてもオリジナル・チップを開発することが可能である.また内部ロジック・リソースのみならず,SerDesやディレイなどI/O専用のロジックもあり高速なシリアル・データ通信も外付けチップなしで実現できる.

本講座では高性能MPUを搭載した最新FPGAで構築した簡単なカメラ・システムにカメラリンク送信I/F機能を実装して外部へのデータ送信を実現する.

※最新FPGAボードも同時に入手できるお得なバンドル・プランもあります.

※同講師によるセミナ「直伝!最新FPGAを使ったビデオ・システムの開発・外部インターフェース(カメラリンク送信)拡張編」を同時にお申込みいただいた方は,受講費用を10%引きいたします.

本セミナの終了時刻は18:00を予定しています

テキスト以外にチュートリアルに最適なサンプル・デザインをお持ち帰りいただけます

1.カメラリンク基礎

1.1 物理的仕様

1.2 データ・フォーマット

1.3 制御コマンド

1.4 処理フロー

2.最新FPGA のI/Oロジック

2.1 バッファ

2.2 ディレイ

2.3 SerDes(デシリアライザ)

2.4 クロック

3.シリアル・データ伝送(受信)での注意点

3.1 ビビット アライメント

3.2 ワード・アライメント

3.3 レシーバチップ

4.開発環境概要

4.1 設計ツールおよび開発ボード

4.2 MPUおよびペリフェラルIP

4.3 システム構成

5.システム拡張実習

5.1 システム・セットアップと動作確認

5.2 カメラリンク送信処理コアの作成とIP化

5.3 インテグレーションとインプリメンテーション

6.質疑応答&まとめ

※進行状況により内容が一部変更となることがあります.

●対象聴講者

・カメラリンク機器を開発したい方

・ビデオ・システムの外部データI/Fに興味のある方

・最新FPGAに搭載されているI/O機能を活用したい方

・既存デザイン(HDL)のIP(再利用パッケージ)化に興味のある方

・HDLおよびC言語の基本的知識必須

・組み込みシステム開発およびFPGA設計(Vivado使用)経験推奨

●講演の目標

・カメラリンクイターフェス受信処理 の仕組みを 理解する

・最新 FPGAのIO機能を理解する

・シリアルデータ伝送(受信側)の ポイントを理解する

・デザインの再利用(IP化)を実践・習得する

セミナ受講時にZyboボードもご購入いただけるバンドル・プランもご用意いたしました.なんと受講料金込みで\54,000-(税込)!

セミナ,ボードをそれぞれ個別購入するよりもお得です.セミナお申込み時にご指定ください.

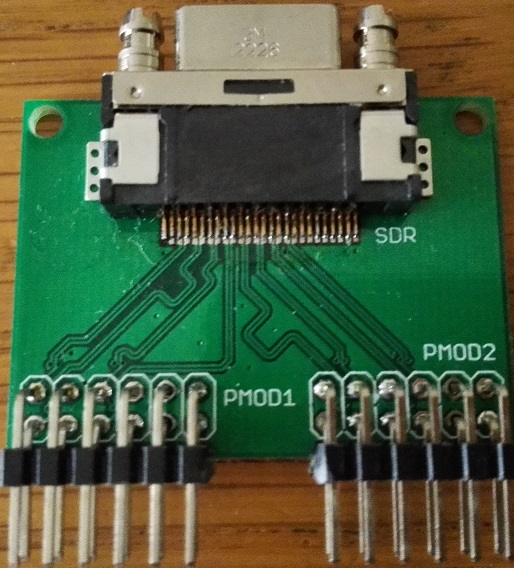

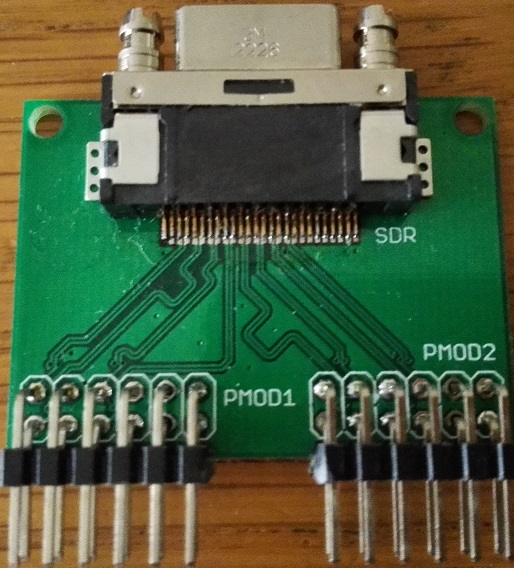

本セミナで使用するカメラリンクコネクタ変換基板

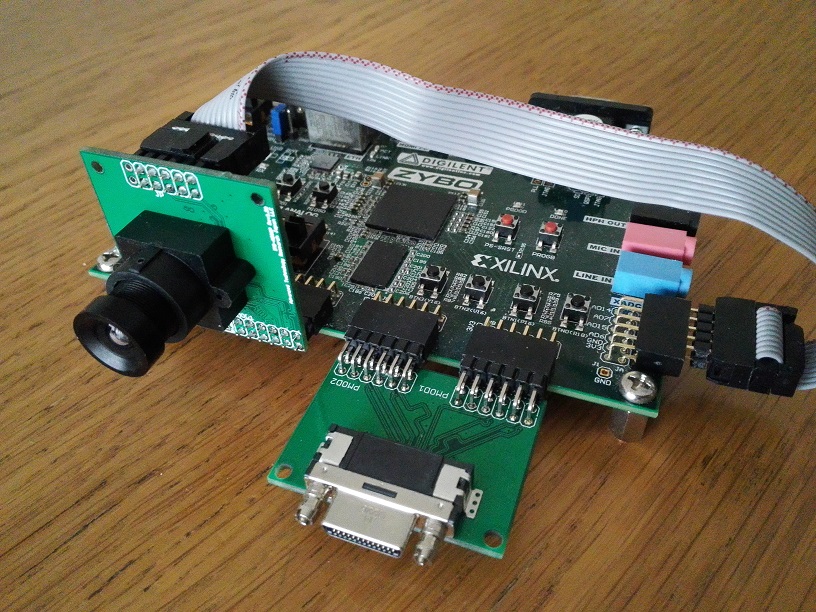

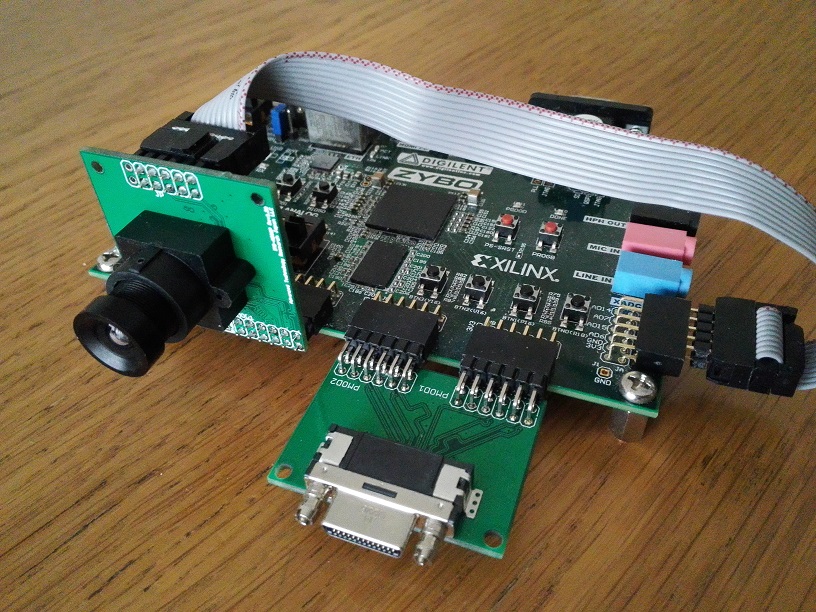

同基板をZyboに装着したようす

1.1 物理的仕様

1.2 データ・フォーマット

1.3 制御コマンド

1.4 処理フロー

2.最新FPGA のI/Oロジック

2.1 バッファ

2.2 ディレイ

2.3 SerDes(デシリアライザ)

2.4 クロック

3.シリアル・データ伝送(受信)での注意点

3.1 ビビット アライメント

3.2 ワード・アライメント

3.3 レシーバチップ

4.開発環境概要

4.1 設計ツールおよび開発ボード

4.2 MPUおよびペリフェラルIP

4.3 システム構成

5.システム拡張実習

5.1 システム・セットアップと動作確認

5.2 カメラリンク送信処理コアの作成とIP化

5.3 インテグレーションとインプリメンテーション

6.質疑応答&まとめ

※進行状況により内容が一部変更となることがあります.

●対象聴講者

・カメラリンク機器を開発したい方

・ビデオ・システムの外部データI/Fに興味のある方

・最新FPGAに搭載されているI/O機能を活用したい方

・既存デザイン(HDL)のIP(再利用パッケージ)化に興味のある方

・HDLおよびC言語の基本的知識必須

・組み込みシステム開発およびFPGA設計(Vivado使用)経験推奨

●講演の目標

・カメラリンクイターフェス受信処理 の仕組みを 理解する

・最新 FPGAのIO機能を理解する

・シリアルデータ伝送(受信側)の ポイントを理解する

・デザインの再利用(IP化)を実践・習得する

セミナ受講時にZyboボードもご購入いただけるバンドル・プランもご用意いたしました.なんと受講料金込みで\54,000-(税込)!

セミナ,ボードをそれぞれ個別購入するよりもお得です.セミナお申込み時にご指定ください.

本セミナで使用するカメラリンクコネクタ変換基板

同基板をZyboに装着したようす

【受講者が持参するもの】

・実機動作演習希望の方はFPGAボード(Zybo,お得な受講時購入バンドルプラン(USBケーブル付)

・※その他実習で使用する機材(パソコン,カメラリンクI/F拡張基板とモニタ)はこちらでご用意いたします.ボードは持参されなくてもツールでの実習はできます.(FPGAボードの貸出はなし)

・2Gバイト以上のUSBメモリ(作業済みデータの持ち帰りを希望される方のみ):実習で使用する例題デザイン・ファイルのアーカイブはサイトからダウンロード配布

・実機動作演習希望の方はFPGAボード(Zybo,お得な受講時購入バンドルプラン(USBケーブル付)

・※その他実習で使用する機材(パソコン,カメラリンクI/F拡張基板とモニタ)はこちらでご用意いたします.ボードは持参されなくてもツールでの実習はできます.(FPGAボードの貸出はなし)

・2Gバイト以上のUSBメモリ(作業済みデータの持ち帰りを希望される方のみ):実習で使用する例題デザイン・ファイルのアーカイブはサイトからダウンロード配布

【講師】

早乙女 勝昭 氏〔アドバンスド・テクノロジー・リサーチ・ジャパン合同会社 President & CXO 〕

FPGAエバンジェリスト.FPGAマガジン#6,#10特集記事執筆.

早乙女 勝昭 氏〔アドバンスド・テクノロジー・リサーチ・ジャパン合同会社 President & CXO 〕

FPGAエバンジェリスト.FPGAマガジン#6,#10特集記事執筆.