長足の進歩を遂げるPLL技術の恩恵で,スマートフォンに代表されるように私たちの生活スタイルは,随分と便利になっている.今では,PLLを構成する個々の回路は極小なワンチップICに取り込まれ,高性能なPLL周波数シンセサイザとして動かすことができる.整数分周だけでなく分数分周方式や,IC化が最も難しい電圧制御発振器(VCO)を内蔵したPLL LSIも登場している.

しかし,PLLの設計は難解で,位相雑音や時間軸の応答特性などを最適化するには,負帰還PLLの動作をしっかりと理解しなければならない.ループ・フィルタの設計を助けるツールを使うにも,それなりの知識が必要となる.

ここでは,PLL Design ツールを使いこなすための基礎知識を解説し,位相雑音特性などを首尾よく設計する方法を例題を用いて説明する.そして,実際に設計したPLL周波数シンセサイザの位相雑音や応答特性を,スペ久トラム・アナライザやオシロスコープで測定して評価する.

1.周波数合成技術とPLL周波数シンセサイザ

1.1 PLL ICの誕生と歴史

1.2 Δ-ΣフラクショナルN PLL ICのしくみ

1.3 VCO内蔵型PLL ICのしくみ

1.4 PLLとDDSシンセサイザのメリット,デメリット

2.PLL技術を使うとこんなことができる

2.1 周波数,位相の同期の取れた発振器を構成

2.2 雑音特性の優れた周波数てい倍回路となる

2.3 フィルタ回路 BPFとして働く

2.4 容易にFM復調できる

3.PLLが出力する位相雑音特性

3.1 発振器位相雑音の発生メカニズム

3.2 高Q発振器(水晶発振器)のSSB位相雑音特性

3.2 低Q発振器(電圧制御発振器)のSSB位相雑音特性

3.3 カットオフ周波数fcとPLLの位相雑音

4.PLL Design ツールを用いて設計する

4.1 PLL Design ツールを使うための基礎知識

4.2 電流出力型チャージポンプPLLのモデル

4.3 SSB位相雑音をシミュレーシュンする

5.フラクショナルPLLを設計して評価する

5.1 微小ステップのPLLを設計する

5.2 周波数を高速に切り替えるには

5.3 ファースト・ロックアップ・モードでサイクル・スリップを抑える

6.PLLの帯域内位相雑音を設計して評価する

6.1 PLL ICで生じる位相雑音

6.2 帯域内位相雑音をシミュレーションして実測する

Appendix PLL設計で発生するトラブル対策

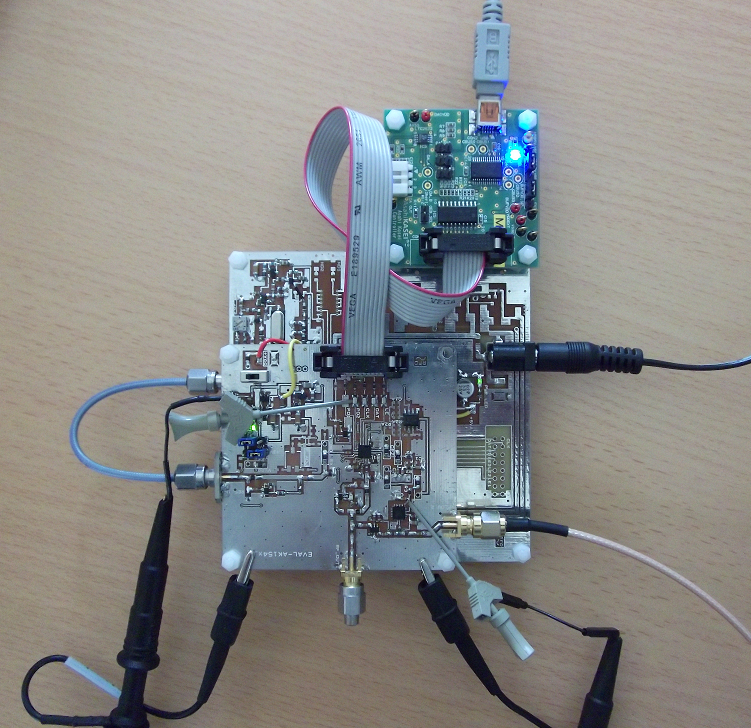

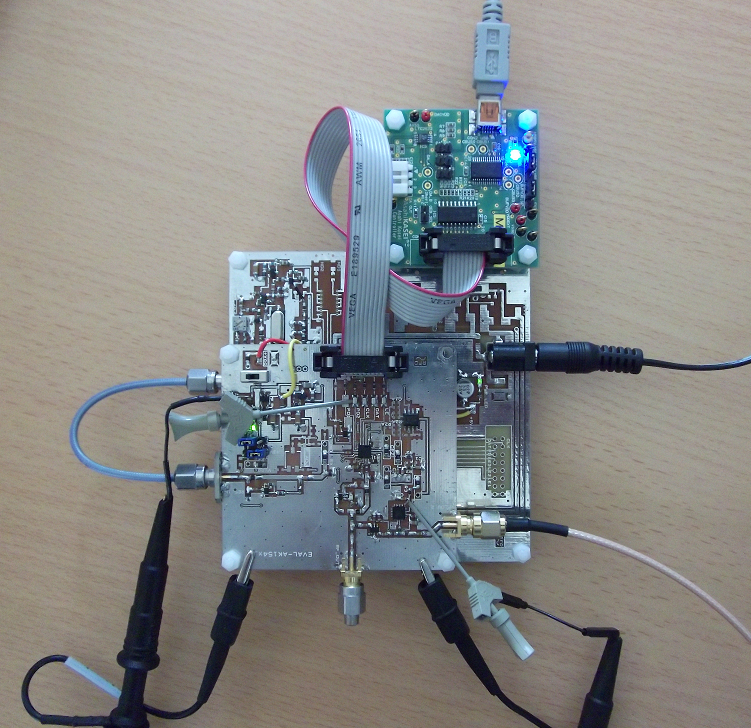

PLL LSI評価ボードの一例

PLL LSI評価ボードの一例

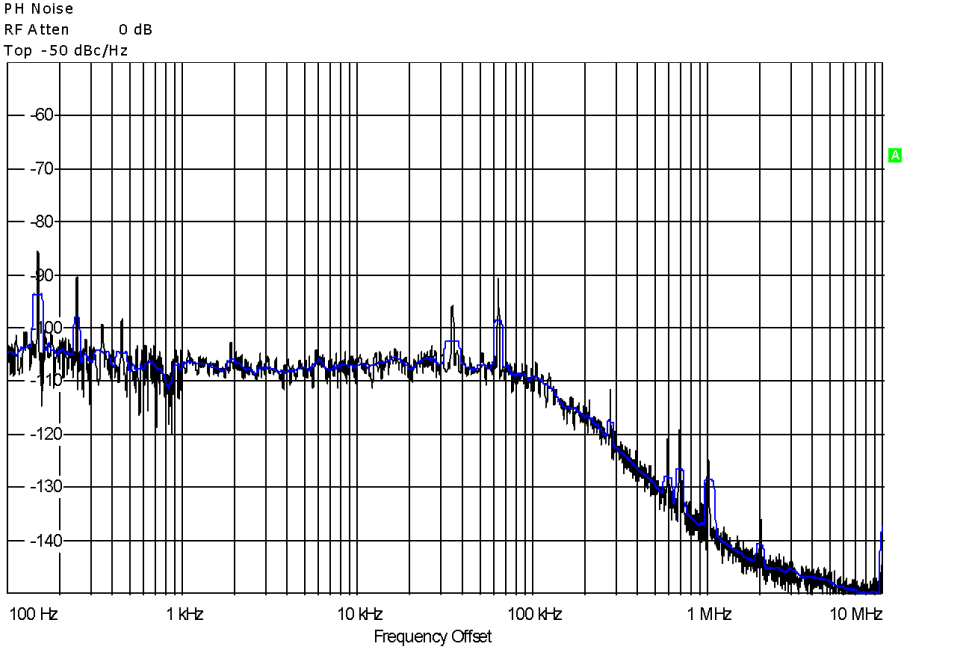

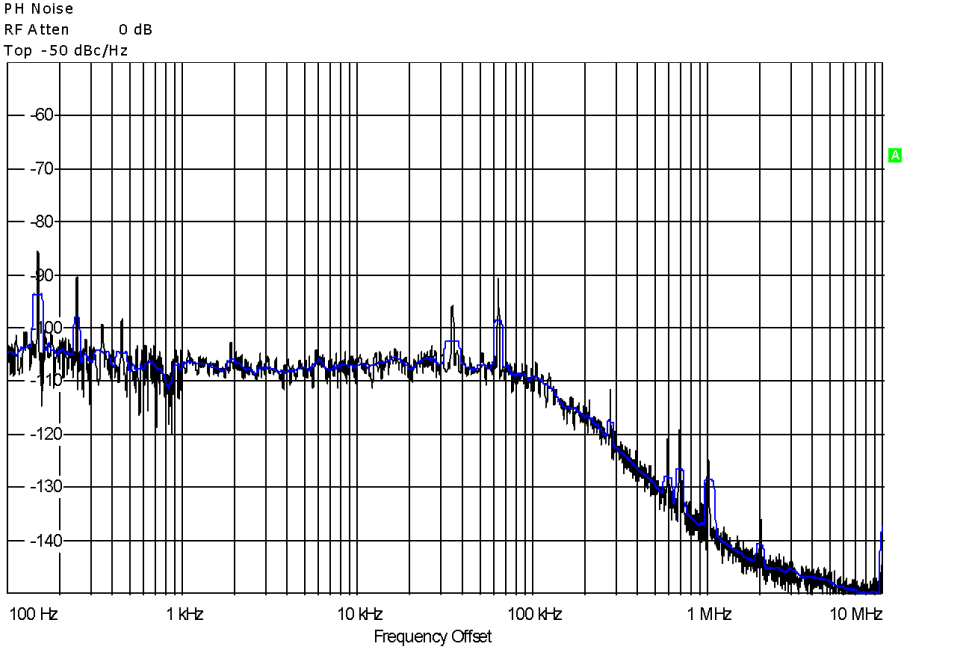

PLL LSIの帯域内位相雑音特性の測定結果の一例●対象聴講者

PLL LSIの帯域内位相雑音特性の測定結果の一例●対象聴講者

・PLL周波数シンセサイザの設計方法をPLL Design ツールと実際の回路を通して学びたい方

・通信機器,電子部品,LSI設計などに従事する技術者で,PLLの設計手法を詳しく知りたい方

・各種PLL LSIを用いて位相雑音や応答特性の最高性能を引き出す最適化設計をめざす方

・PLL技術のさまざまな分野における応用を考えている方

・同講師によるせみな「PLL周波数シンセサイザ入門」を受講していることが望ましい

●講演の目標

・周波数合成技術の発展と最新のPLL ICによる周波数シンセサイザの性能と応用情報が得られる

・PLL Design ツールを使いこなすための基礎知識が得られる

・電圧制御発振器や水晶発振器の位相雑音,およびPLLの位相雑音合成技術を理解できる

・フラクショナルPLLの設計方法と応答特性の実際,および改善方法を理解できる

・PLLの帯域内位相雑音を低減する方法を理解できる

●参考文献

・小宮 浩;「

特集 PLL周波数シンセサイザの実用設計法」RFワールド No.20,CQ出版社,2012年11月.

・小宮 浩;

高周波PLL回路のしくみと設計法,CQ出版社,2009年10月.

・RFデザインノート(講師のWebサイト),

http://gate.ruru.ne.jp/rfdn/