近年PLL技術は,テレビ,パソコン,携帯電話などの一般電気製品にも広く使われ,欠くことのできない技術である.一例として,映像や音声の情報信号は高周波の搬送波に乗せて(変調して)送られるが,この搬送波はPLL周波数シンセサイザで作られる信号である.もし,この信号が揺らげば,当然情報が欠けて正しく伝わらない.ベクトル多値変調の時代に入り,ますます純度の高い信号が必要とされ,加えて周波数切り替えの高速化もPLL技術に求められている.

ここでは,PLL周波数シンセサイザ評価ボードとスペクトラム・アナライザを用いて,高周波PLL回路のしくみとループ定数と位相雑音の関係などを実演を通して学ぶ.まず,PLL技術の紹介に続き,PLLを構成する個々の回路の動作を知る.位相雑音の発生原因と重要性,時間軸での応答特性への理解を深める.次に,PLL負帰還回路が不安定になる原因を考え,最適なループ定数の決め方を紹介する.

1.PLL周波数シンセサイザとは

1.1 新たな周波数を作り出す周波数シンセサイザ

1.2 分周数Nとノイズの関係

1.3 位相雑音と基準信号漏れによるスプリアス

2.PLLの基本動作を理解する

2.1 周波数が一定に保たれるしくみ

2.2 PLLを構成する基本回路

2.3 RF帯でPLL周波数シンセサイザを構成するには

2.4 整数と分数分周 PLL周波数シンセサイザの比較

3.位相雑音の少ないPLL周波数シンセサイザを設計する

3.1 位相雑音の重要性

3.2 RMS位相誤差と位相ジッタと位相雑音

3.2 位相雑音を定量的に表す

3.3 PLLの位相雑音モデル

4.PLLの時間軸での応答特性

4.1 応答特性の理想と実際

4.2 周波数を高速に切り替えるには

5.ループ・フィルタ設計の基礎知識

5.1 PLL周波数シンセサイザの鍵はループ・フィルタ

5.2 帰還回路の動作を理解する

5.3 負帰環回路が不安定になる原因

6.最適なループ・フィルタ定数を得る

6.1 PLLの開ループ伝達関数を求める

6.2 ラグ・フィルタとラグ・リード・フィルタを用いたPLLの欠点

6.3 3次形でPLLを設計する

6.4 決定したループ・フィルタ定数でのSSB位相雑音特性

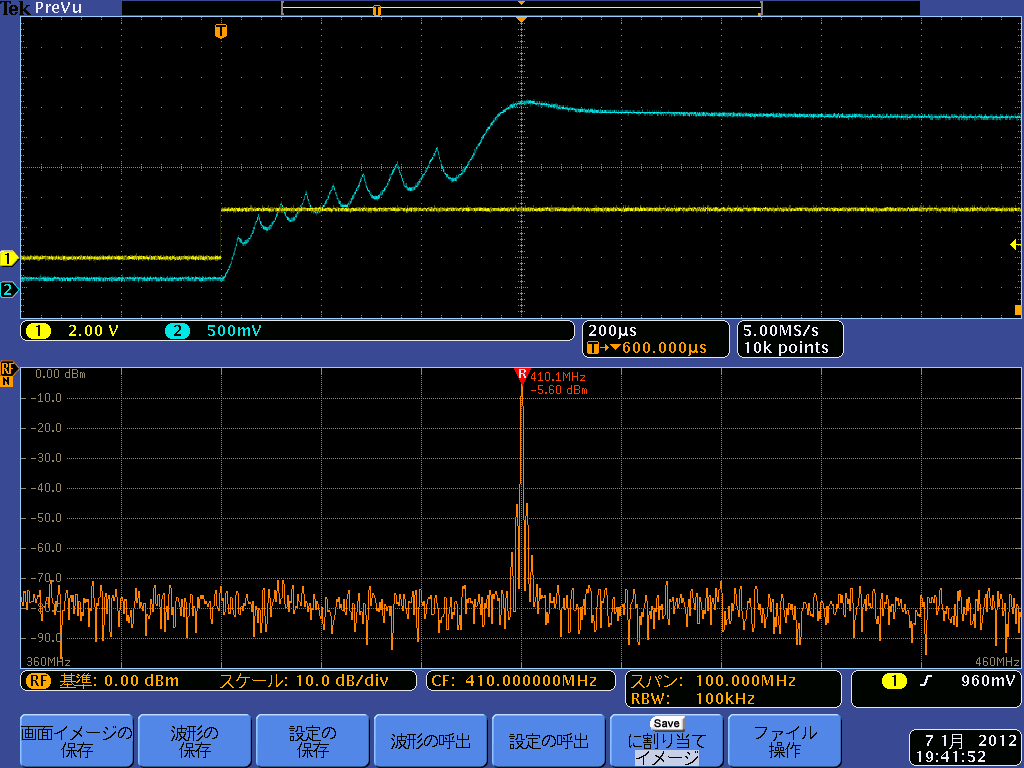

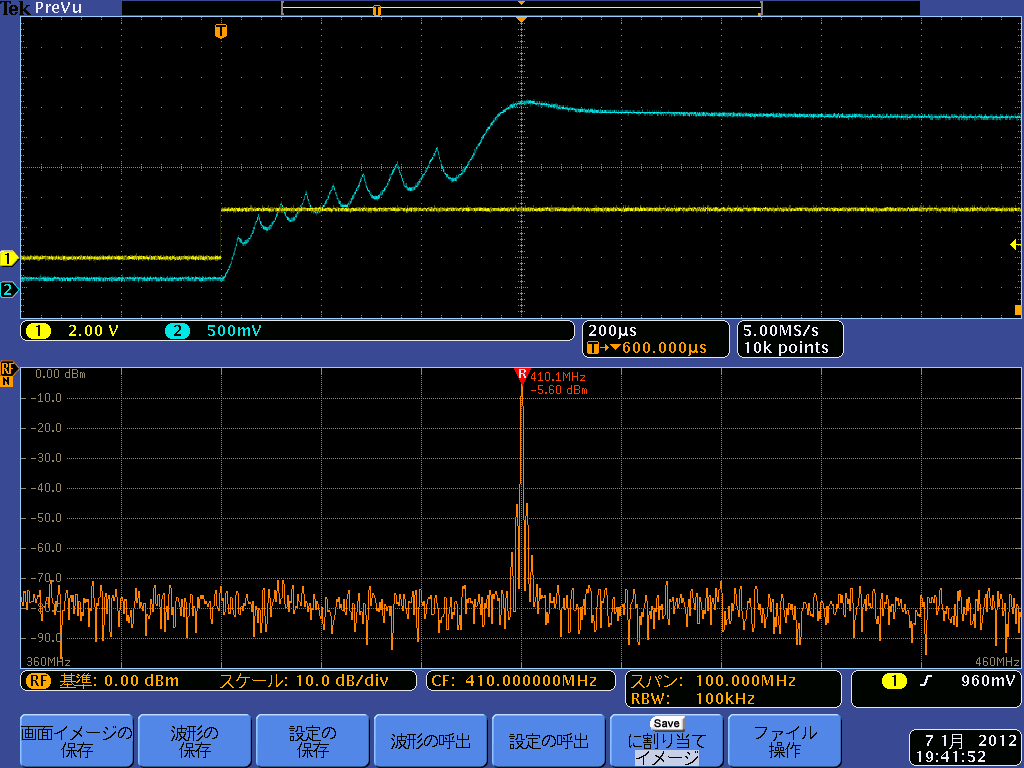

PLLの時間軸と周波数軸の過渡応答特性例

PLLの時間軸と周波数軸の過渡応答特性例

ループ・フィルタ定数の違いによる位相雑音特性の変化●対象聴講者

ループ・フィルタ定数の違いによる位相雑音特性の変化●対象聴講者

・PLL周波数シンセサイザの構成やしくみを実際の回路を通して学びたい方(学生を含む)

・通信機器,電子部品,LSI設計などに従事する技術者で,PLL技術に触れてみたい方

・PLL周波数シンセサイザのさらなる低位相雑音化とループ・フィルタの最適化設計をめざす方

・PLL技術のさまざまな分野における応用を考えている方

●講演の目標

・PLL技術の全般とPLLを構成する電圧制御発振器(VCO),基準源発振器(VCXO),位相比較器,分周器などの動作を理解できる

・PLL負帰還動作を理解し,時間軸を含めて安定に動作させる知識が得られる

・位相雑音やスプリアスの発生要因と評価方法を知ることができる

・さまざまな形に位相雑音を合成するループ・フィルタ設計の基礎が分かる

●参考文献

・小宮 浩;「

特集 PLL周波数シンセサイザの実用設計法」RFワールド No.20,CQ出版社,2012年11月.

・小宮 浩;

高周波PLL回路のしくみと設計法,CQ出版社,2009年10月.

・RFデザインノート(講師のWebサイト),

http://gate.ruru.ne.jp/rfdn/