実習・論理回路の設計からFPGAの動作まで [ディジタル回路設計入門シリーズ1]

実習・論理回路の設計からFPGAの動作まで [ディジタル回路設計入門シリーズ1]

|

|

【開催日】2017年7月27日(木) ~ 2017年7月28日(金) 10:00-17:00 2日コース

【セミナNo.】ES17-0078 【受講料】37,000円(税込)

【会場】東京・巣鴨 CQ出版社セミナ・ルーム [地図]

【セミナNo.】ES17-0078 【受講料】37,000円(税込)

【会場】東京・巣鴨 CQ出版社セミナ・ルーム [地図]

この講座では,2日間でディジタル回路の開発・設計に必要な知識やノウハウについて,実務経験豊富な講師が実習を取り入れながらていねいに解説する.

1日目は論理(ディジタル)回路設計の基本(ブール代数,論理演算,論理回路,記憶回路)を学習し,トランジスタ・CMOSの動作と回路素子(IC)を使うときのタイミング・ノイズなどの注意事項を学習する.学習したブール代数,論理演算を応用したスイッチのチャタリング除去回路の設計を行う.この回路は2日目のVerilog言語,ModelSimを学習してから,トレーニング・ボード上でスイッチのチャタリングの確認とチャタリング除去の実習を行う. 1日目の午後からはAltera社から無償で提供されたFPGA設計ツール(Quartus Prime)を使いFPGA(MAX10)が実装されたトレーニング・ボードを使いながらハードウエア記述言語(VerilogHDL)とFPGAにディジタル回路を書き込み,FPGAの基本的な使い方とVerilogHDL記述を学習する.

2日目は1日目に引き続き,設計上の注意事項を説明しながら,VerilogHDLの順序回路,階層設計,ModelSimを使った動作シミュレーションを行う(実習).

※ 実習で使用するパソコンおよび,FPGAボード(DE10-Lite)はCQ出版社が用意します.

1日目は論理(ディジタル)回路設計の基本(ブール代数,論理演算,論理回路,記憶回路)を学習し,トランジスタ・CMOSの動作と回路素子(IC)を使うときのタイミング・ノイズなどの注意事項を学習する.学習したブール代数,論理演算を応用したスイッチのチャタリング除去回路の設計を行う.この回路は2日目のVerilog言語,ModelSimを学習してから,トレーニング・ボード上でスイッチのチャタリングの確認とチャタリング除去の実習を行う. 1日目の午後からはAltera社から無償で提供されたFPGA設計ツール(Quartus Prime)を使いFPGA(MAX10)が実装されたトレーニング・ボードを使いながらハードウエア記述言語(VerilogHDL)とFPGAにディジタル回路を書き込み,FPGAの基本的な使い方とVerilogHDL記述を学習する.

2日目は1日目に引き続き,設計上の注意事項を説明しながら,VerilogHDLの順序回路,階層設計,ModelSimを使った動作シミュレーションを行う(実習).

※ 実習で使用するパソコンおよび,FPGAボード(DE10-Lite)はCQ出版社が用意します.

[1日目]

1.論理(ディジタル)回路設計の基本(ブール代数,論理演算,論理回路,記憶回路)を学習し,トランジスタ・CMOSの動作と回路素子(IC)を使うときのタイミング・ノイズなどの注意事項とスイッチのチャタリング除去のディジタル回路を学習する.

2.QuartusPrimeのVerilog開発環境使い,VerilogHDL文法の基本を学習し,トレーニング・ボード上のFPGAに回路を書き込み動作確認まで行う(実習)

[2日目]

3.1日目に続き,VerilogHDLの順序回路,階層設計を学習する(実習)

4.VerilogHDLのalways文を使った組合せ回路記述は設計ミスが発生しやすいため,この対策としてSystemVerilog記述と大規模設計に適したステートマシンの設計手法を学習する(実習)

5. ModelSimの使い方を学習し,Verilogで記述されたモジュールの動作確認をModelSimで行う

6. スイッチのチャタリング除去回路は実用的なVerilog記述とModelSimの使い方を実習する

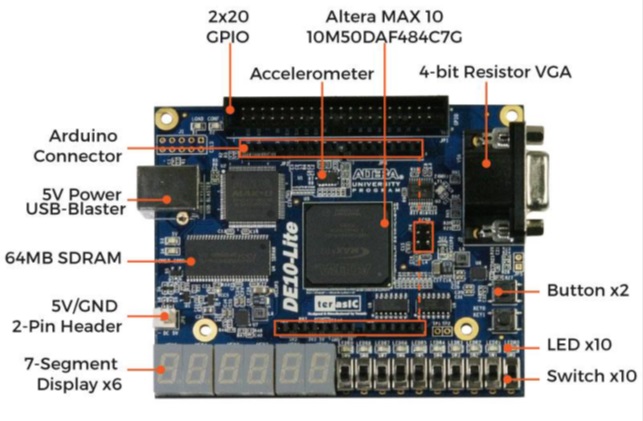

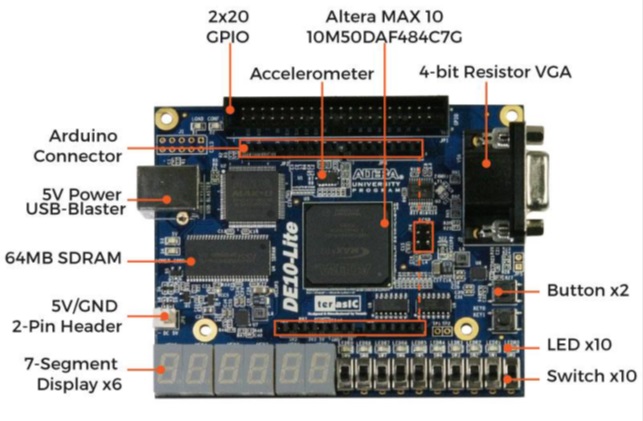

※ トレーニング・ボードとして,MAX10:10M50DAF484C7Gが実装されているFPGAボード(DE10-Lite)を使います.

本セミナで使用するFPGA(MAX10)が実装されたトレーニング・ボード(DE10-Lite)

DE10-Liteは,以下の部品を搭載しています.

・MAX10 10M50DAF484C7G Device

・Integrated dual ADCs

・50K programmable logic elements

・1,638 Kbits M9K Memory

・5,888 Kbits user flash memory

・144 18 × 18 Multiplier

・4 PLLs

・50-MHz 発振器

・On-Board USB Blaster

・64MB SDRAM, x16 bits data bus

・Arduino Uno R3 Connector, including six ADC channels

●対象聴講者

・基本論理素子(AND,OR,NOT,FF)の基本動作を知っている方

・2進数,10進数,16進数を知っている方

・ブール代数について教科書などで学んだことがある方

・Windowsパソコンの基本操作ができる方

1.論理(ディジタル)回路設計の基本(ブール代数,論理演算,論理回路,記憶回路)を学習し,トランジスタ・CMOSの動作と回路素子(IC)を使うときのタイミング・ノイズなどの注意事項とスイッチのチャタリング除去のディジタル回路を学習する.

2.QuartusPrimeのVerilog開発環境使い,VerilogHDL文法の基本を学習し,トレーニング・ボード上のFPGAに回路を書き込み動作確認まで行う(実習)

[2日目]

3.1日目に続き,VerilogHDLの順序回路,階層設計を学習する(実習)

4.VerilogHDLのalways文を使った組合せ回路記述は設計ミスが発生しやすいため,この対策としてSystemVerilog記述と大規模設計に適したステートマシンの設計手法を学習する(実習)

5. ModelSimの使い方を学習し,Verilogで記述されたモジュールの動作確認をModelSimで行う

6. スイッチのチャタリング除去回路は実用的なVerilog記述とModelSimの使い方を実習する

※ トレーニング・ボードとして,MAX10:10M50DAF484C7Gが実装されているFPGAボード(DE10-Lite)を使います.

本セミナで使用するFPGA(MAX10)が実装されたトレーニング・ボード(DE10-Lite)

DE10-Liteは,以下の部品を搭載しています.

・MAX10 10M50DAF484C7G Device

・Integrated dual ADCs

・50K programmable logic elements

・1,638 Kbits M9K Memory

・5,888 Kbits user flash memory

・144 18 × 18 Multiplier

・4 PLLs

・50-MHz 発振器

・On-Board USB Blaster

・64MB SDRAM, x16 bits data bus

・Arduino Uno R3 Connector, including six ADC channels

●対象聴講者

・基本論理素子(AND,OR,NOT,FF)の基本動作を知っている方

・2進数,10進数,16進数を知っている方

・ブール代数について教科書などで学んだことがある方

・Windowsパソコンの基本操作ができる方

【講師】

萬代 慶昭 氏〔バンテクノ 〕

1968年,東芝に入社.通信インターフェース装置のハードウェア設計などに従事.2003年,東芝を退職し,バンテクノを設立.マイコン組み込み装置に使われるFPGA設計の受託に従事.

萬代 慶昭 氏〔バンテクノ 〕

1968年,東芝に入社.通信インターフェース装置のハードウェア設計などに従事.2003年,東芝を退職し,バンテクノを設立.マイコン組み込み装置に使われるFPGA設計の受託に従事.