実習・直伝!最新FPGAを使ったビデオ・システムの開発(画像フィルタ設計編)

実習・直伝!最新FPGAを使ったビデオ・システムの開発(画像フィルタ設計編)

|

|

【開催日】2014年8月27日(水) 10:00-18:00 1日コース

【セミナNo.】ES14-0078 【受講料】29,000円(税込)

【会場】東京・巣鴨 CQ出版社セミナ・ルーム [地図]

【セミナNo.】ES14-0078 【受講料】29,000円(税込)

【会場】東京・巣鴨 CQ出版社セミナ・ルーム [地図]

近年,FPGAデバイスのめざましい発展(性能向上,大規模化,ローコスト化)により,従来ASICで行っていた複雑なシステム・オン・チップ(SoC)の実現をデスクトップ上で手軽に実現できるようになってきた.

また,MPU等のIP(再利用可能設計済み回路)を使用することによりハードウェア設計の深い知識がなくてもオリジナル・チップを開発することが可能である.

本講座では簡単なカメラ・システムを例にAptina社製イメージ・センサ・モジュール(300万画素品使用)とXilinx社製Zynqデバイスを搭載したDigilent社製FPGAボード(ZyboまたはZedboard)を使用して,最適な画像フィルタ処理(FIRフィルタ)回路の設計方法を実際に演習を行いそのポイントを習得する.

また,ザイリンクス社最新統合設計環境「Vivado」(バージョン2014.2)で提供されるC言語設計高位合成ツール(HLS)も適用してそのアルゴリズム検証からIP化までを'非'HDLで行う.

また,MPU等のIP(再利用可能設計済み回路)を使用することによりハードウェア設計の深い知識がなくてもオリジナル・チップを開発することが可能である.

本講座では簡単なカメラ・システムを例にAptina社製イメージ・センサ・モジュール(300万画素品使用)とXilinx社製Zynqデバイスを搭載したDigilent社製FPGAボード(ZyboまたはZedboard)を使用して,最適な画像フィルタ処理(FIRフィルタ)回路の設計方法を実際に演習を行いそのポイントを習得する.

また,ザイリンクス社最新統合設計環境「Vivado」(バージョン2014.2)で提供されるC言語設計高位合成ツール(HLS)も適用してそのアルゴリズム検証からIP化までを'非'HDLで行う.

セミナ受講時にZyboボードもご購入いただけるバンドル・プランもご用意いたしました.なんと受講料金込みで\50,000-(税込)!

USBケーブルも付属して(通常販売品は付属なし),セミナ,ボードをそれぞれ個別購入するよりもかなりお得です.セミナお申込み時にご指定ください.

また,期間・数量限定でボードと付属品を収納・持ち運びに便利なプラスチック・ケースとポーチを差し上げます.(なくなり次第終了)ぜひこの機会をお見逃しなく!

1.画像フィルタ基礎

1.1 2DFIR(微分)フィルタ概要

1.2 演算ツリー

1.3 各種係数(平滑化,先鋭化,ラプラシアン,ガウシアンなど)

2.最新FPGAのデバイス・アーキテクチャ

3.1 ASIC設計との違いと注意点

3.2 内蔵ハード・リソース(RAM,演算器,シフト・レジスタなど)

3.高位合成ツール(Vivado HLS)

3.1 開発フロー

3.2 生成回路最適化(ディレクティブ適用)

4.システム構築実習

4.1 ベース・システムの構成とデータ・フロー・レビュー

4.2 ソフトウェア処理での実装とアルゴリズム検証

4.3 ハードウェア化するための改良(Cソース修正)

4.4 高位合成によるRTL生成とIPパッケージ化(MPUバスI/Fの付加)

4.5 ベース・システムへの生成したコアの組込

4.5 MPUからのコア制御ソフトウェアの作成と動作確認

5.まとめ(デモ)&質疑応答

※ パソコンやカメラ・キットなど,実習に使用する機材はこちらでご用意いたします.

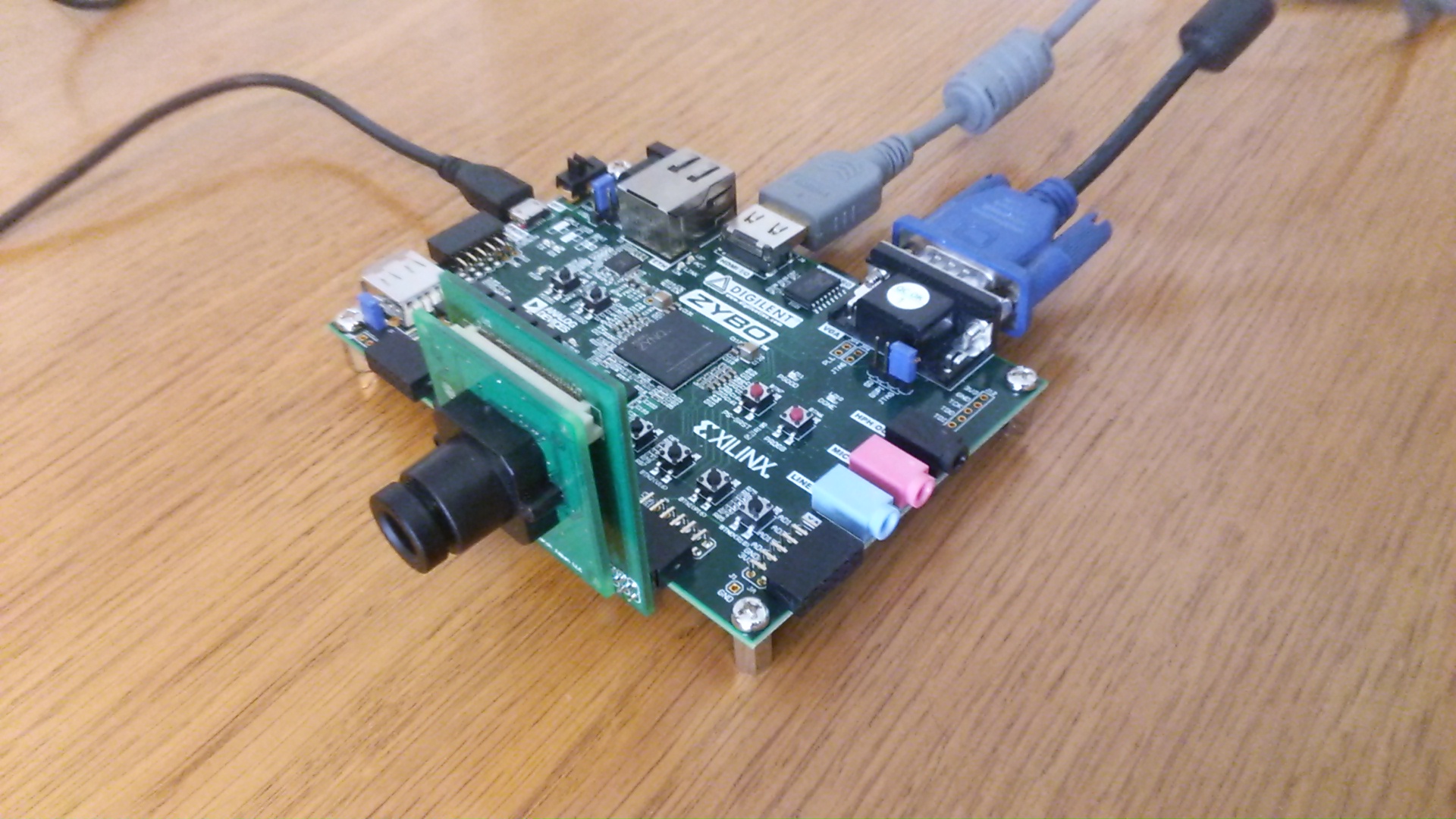

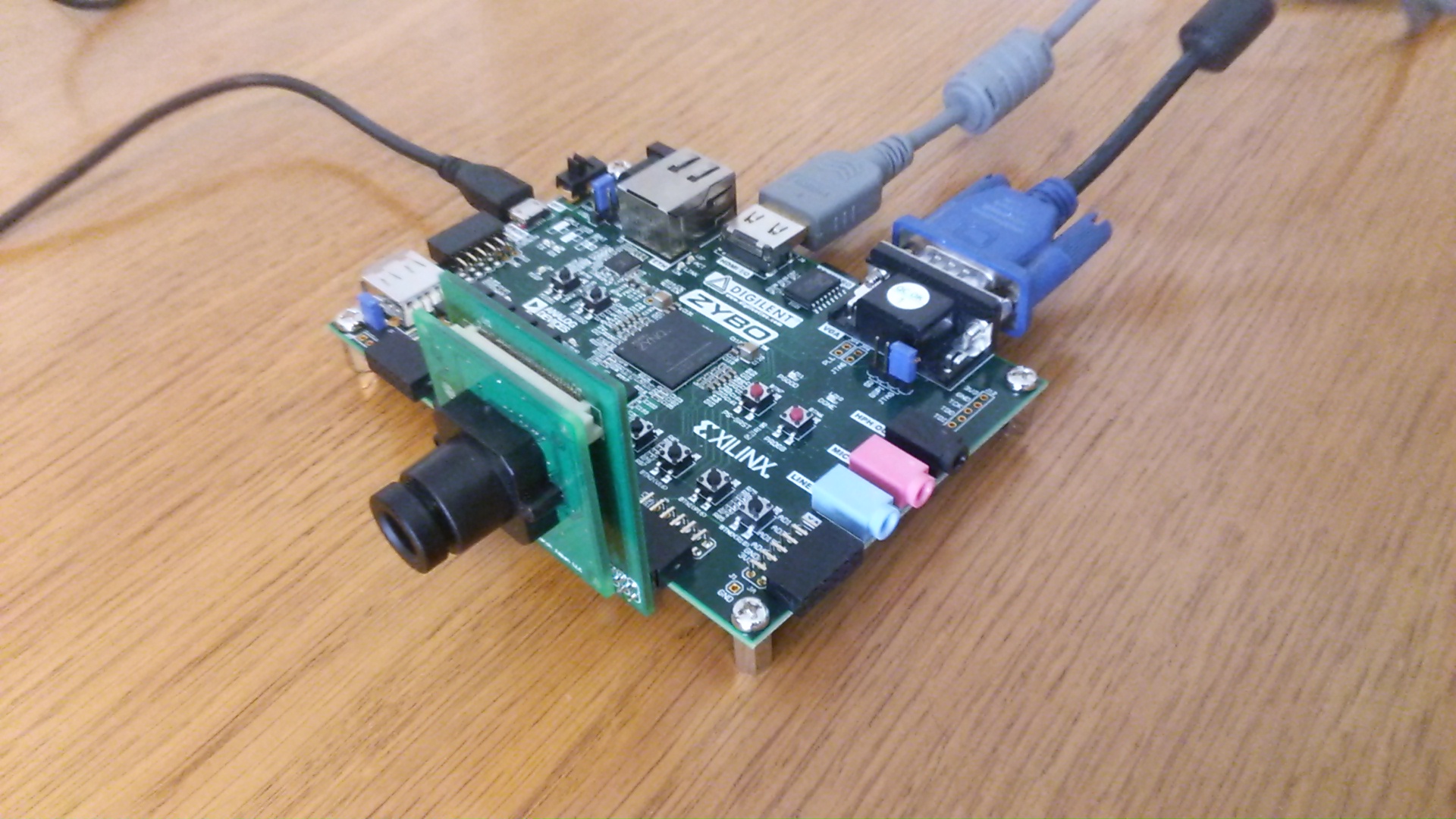

本セミナで使用する組み込みカメラの開発キット-Zybo版(Aptina社のイメージ・センサとXilinx社のFPGAを搭載)

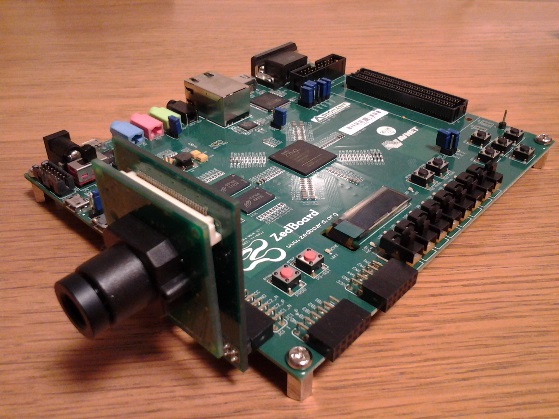

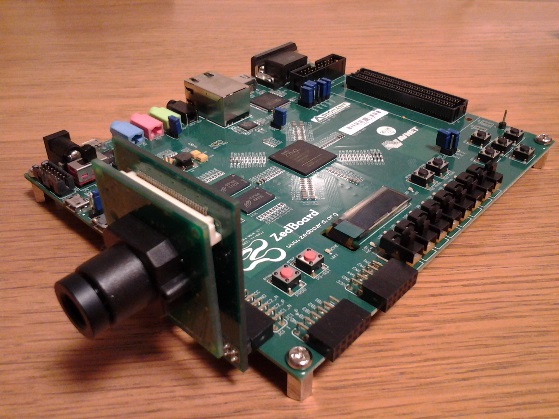

同上-Zedboard版

●対象聴講者

・低コストにビデオシステムを開発しようとしている方

・FPGAでのビデオ信号処理の実装方法の詳細を知りたい方

・C言語設計および非HDL設計に興味のある方

・FPGAに搭載されたMPUを活用したい方

※C言語と組込システムの基礎知識必須

※HDLでのハード設計経験推奨

※同講師によるセミナ実習・直伝!最新FPGAを使ったビデオ・システムの開発(プラット・フォーム構築編)を既に受講いただいた方は,受講費用を10%引きいたします.(IPベース設計にもご興味のある方は同講座も合わせてのご受講をお薦め致します)

●講演の目標

・画像フィルタの理解

・最新FPGAの応用方法の理解

・カスタムロジックのIPコア化とMPUとのインターフェース方法の理解

・C言語ベース・ハードウェア設計方法の理解

※ 本セミナの終了時刻は18:00を予定しています.

USBケーブルも付属して(通常販売品は付属なし),セミナ,ボードをそれぞれ個別購入するよりもかなりお得です.セミナお申込み時にご指定ください.

また,期間・数量限定でボードと付属品を収納・持ち運びに便利なプラスチック・ケースとポーチを差し上げます.(なくなり次第終了)ぜひこの機会をお見逃しなく!

1.画像フィルタ基礎

1.1 2DFIR(微分)フィルタ概要

1.2 演算ツリー

1.3 各種係数(平滑化,先鋭化,ラプラシアン,ガウシアンなど)

2.最新FPGAのデバイス・アーキテクチャ

3.1 ASIC設計との違いと注意点

3.2 内蔵ハード・リソース(RAM,演算器,シフト・レジスタなど)

3.高位合成ツール(Vivado HLS)

3.1 開発フロー

3.2 生成回路最適化(ディレクティブ適用)

4.システム構築実習

4.1 ベース・システムの構成とデータ・フロー・レビュー

4.2 ソフトウェア処理での実装とアルゴリズム検証

4.3 ハードウェア化するための改良(Cソース修正)

4.4 高位合成によるRTL生成とIPパッケージ化(MPUバスI/Fの付加)

4.5 ベース・システムへの生成したコアの組込

4.5 MPUからのコア制御ソフトウェアの作成と動作確認

5.まとめ(デモ)&質疑応答

※ パソコンやカメラ・キットなど,実習に使用する機材はこちらでご用意いたします.

本セミナで使用する組み込みカメラの開発キット-Zybo版(Aptina社のイメージ・センサとXilinx社のFPGAを搭載)

同上-Zedboard版

●対象聴講者

・低コストにビデオシステムを開発しようとしている方

・FPGAでのビデオ信号処理の実装方法の詳細を知りたい方

・C言語設計および非HDL設計に興味のある方

・FPGAに搭載されたMPUを活用したい方

※C言語と組込システムの基礎知識必須

※HDLでのハード設計経験推奨

※同講師によるセミナ実習・直伝!最新FPGAを使ったビデオ・システムの開発(プラット・フォーム構築編)を既に受講いただいた方は,受講費用を10%引きいたします.(IPベース設計にもご興味のある方は同講座も合わせてのご受講をお薦め致します)

●講演の目標

・画像フィルタの理解

・最新FPGAの応用方法の理解

・カスタムロジックのIPコア化とMPUとのインターフェース方法の理解

・C言語ベース・ハードウェア設計方法の理解

※ 本セミナの終了時刻は18:00を予定しています.

【受講者が持参するもの】

・・FPGAボード(ZyboまたはZedboard):Zybo推奨(お得な受講時同時購入バンドルプランをご利用ください)

※FPGAボードを持参しなくてもセミナ受講は可能です.(PCでの実習もあり)詳細は申込時にお問い合わせください.

・2Gバイト以上のUSBメモリ(作業済みデータの持ち帰りを希望される方のみ):実習で使用する例題デザイン・ファイルのアーカイブはDVDで配布

・その他実習に必要な機材(PC※,イメージ・センサ・モジュール,モニタ)は事務局で用意します.

※PCはお持込も可能です.(ただし,指定バージョンのザイリンクス設計ツールを事前にインストールして動作確認をしておいてください.詳細はお申込み時にお問い合わせください)

・・FPGAボード(ZyboまたはZedboard):Zybo推奨(お得な受講時同時購入バンドルプランをご利用ください)

※FPGAボードを持参しなくてもセミナ受講は可能です.(PCでの実習もあり)詳細は申込時にお問い合わせください.

・2Gバイト以上のUSBメモリ(作業済みデータの持ち帰りを希望される方のみ):実習で使用する例題デザイン・ファイルのアーカイブはDVDで配布

・その他実習に必要な機材(PC※,イメージ・センサ・モジュール,モニタ)は事務局で用意します.

※PCはお持込も可能です.(ただし,指定バージョンのザイリンクス設計ツールを事前にインストールして動作確認をしておいてください.詳細はお申込み時にお問い合わせください)

【講師】

早乙女 勝昭 氏〔アドバンスド・テクノロジー・リサーチ・ジャパン合同会社 President & CXO 〕

FPGAエバンジェリスト.FPGAマガジン#6,#10特集記事執筆.

早乙女 勝昭 氏〔アドバンスド・テクノロジー・リサーチ・ジャパン合同会社 President & CXO 〕

FPGAエバンジェリスト.FPGAマガジン#6,#10特集記事執筆.